Tóm tắt về tấm wafer SiC

Tấm wafer cacbua silic (SiC)Các vật liệu bán dẫn đã trở thành chất nền được lựa chọn cho các thiết bị điện tử công suất cao, tần số cao và nhiệt độ cao trong các lĩnh vực ô tô, năng lượng tái tạo và hàng không vũ trụ. Danh mục sản phẩm của chúng tôi bao gồm các loại đa hình và sơ đồ pha tạp chính—4H pha tạp nitơ (4H-N), bán cách điện độ tinh khiết cao (HPSI), 3C pha tạp nitơ (3C-N) và 4H/6H loại p (4H/6H-P)—được cung cấp ở ba cấp chất lượng: PRIME (chất nền được đánh bóng hoàn toàn, chất lượng thiết bị), DUMMY (được mài hoặc không đánh bóng để thử nghiệm quy trình) và RESEARCH (lớp màng mỏng tùy chỉnh và cấu hình pha tạp cho R&D). Đường kính wafer trải rộng từ 2″, 4″, 6″, 8″ và 12″ để phù hợp với cả các thiết bị cũ và các nhà máy sản xuất tiên tiến. Chúng tôi cũng cung cấp các khối tinh thể đơn và các tinh thể mầm được định hướng chính xác để hỗ trợ quá trình nuôi cấy tinh thể nội bộ.

Các tấm wafer 4H-N của chúng tôi có mật độ hạt tải điện từ 1×10¹⁶ đến 1×10¹⁹ cm⁻³ và điện trở suất từ 0,01–10 Ω·cm, mang lại độ linh động điện tử tuyệt vời và điện trường đánh thủng trên 2 MV/cm—lý tưởng cho các điốt Schottky, MOSFET và JFET. Các chất nền HPSI có điện trở suất vượt quá 1×10¹² Ω·cm với mật độ vi ống dưới 0,1 cm⁻², đảm bảo rò rỉ tối thiểu cho các thiết bị RF và vi sóng. 3C-N dạng khối, có sẵn ở định dạng 2″ và 4″, cho phép dị epitaxy trên silicon và hỗ trợ các ứng dụng quang tử và MEMS mới. Các tấm wafer 4H/6H-P loại P, được pha tạp nhôm đến 1×10¹⁶–5×10¹⁸ cm⁻³, tạo điều kiện thuận lợi cho các kiến trúc thiết bị bổ sung.

Các tấm wafer SiC, wafer PRIME trải qua quá trình đánh bóng hóa học-cơ học để đạt độ nhám bề mặt RMS <0,2 nm, độ biến thiên tổng độ dày dưới 3 µm và độ cong <10 µm. Các chất nền DUMMY giúp tăng tốc quá trình lắp ráp và kiểm tra đóng gói, trong khi các wafer RESEARCH có độ dày lớp epitaxy từ 2–30 µm và được pha tạp theo yêu cầu. Tất cả các sản phẩm đều được chứng nhận bằng nhiễu xạ tia X (đường cong dao động <30 arcsec) và quang phổ Raman, cùng với các thử nghiệm điện – đo Hall, lập hồ sơ C–V và quét vi ống – đảm bảo tuân thủ tiêu chuẩn JEDEC và SEMI.

Các khối tinh thể có đường kính lên đến 150 mm được nuôi cấy thông qua phương pháp PVT và CVD với mật độ sai lệch dưới 1×10³ cm⁻² và số lượng vi ống thấp. Các tinh thể mầm được cắt trong phạm vi 0,1° so với trục c để đảm bảo quá trình nuôi cấy có thể tái tạo và năng suất cắt lát cao.

Bằng cách kết hợp nhiều loại tinh thể, biến thể pha tạp, cấp chất lượng, kích thước tấm wafer SiC và quy trình sản xuất tinh thể tròn và tinh thể mầm nội bộ, nền tảng chất nền SiC của chúng tôi giúp tối ưu hóa chuỗi cung ứng và đẩy nhanh quá trình phát triển thiết bị cho xe điện, lưới điện thông minh và các ứng dụng trong môi trường khắc nghiệt.

Tóm tắt về tấm wafer SiC

Tấm wafer cacbua silic (SiC)Vật liệu nền SiC đã trở thành lựa chọn hàng đầu cho các thiết bị điện tử công suất cao, tần số cao và nhiệt độ cao trong các lĩnh vực ô tô, năng lượng tái tạo và hàng không vũ trụ. Danh mục sản phẩm của chúng tôi bao gồm các loại đa hình và sơ đồ pha tạp chính—4H pha tạp nitơ (4H-N), bán cách điện độ tinh khiết cao (HPSI), 3C pha tạp nitơ (3C-N) và 4H/6H loại p (4H/6H-P)—được cung cấp ở ba cấp chất lượng: tấm wafer SiCPRIME (chất nền được đánh bóng hoàn toàn, đạt tiêu chuẩn thiết bị), DUMMY (được mài hoặc không đánh bóng để thử nghiệm quy trình) và RESEARCH (lớp màng mỏng tùy chỉnh và cấu hình pha tạp cho nghiên cứu và phát triển). Đường kính tấm wafer SiC trải rộng từ 2″, 4″, 6″, 8″ và 12″ để phù hợp với cả các thiết bị cũ và các nhà máy sản xuất tiên tiến. Chúng tôi cũng cung cấp các khối tinh thể đơn và tinh thể mầm định hướng chính xác để hỗ trợ quá trình nuôi cấy tinh thể nội bộ.

Các tấm wafer SiC 4H-N của chúng tôi có mật độ hạt tải điện từ 1×10¹⁶ đến 1×10¹⁹ cm⁻³ và điện trở suất từ 0,01–10 Ω·cm, mang lại độ linh động điện tử tuyệt vời và điện trường đánh thủng trên 2 MV/cm—lý tưởng cho các điốt Schottky, MOSFET và JFET. Các chất nền HPSI có điện trở suất vượt quá 1×10¹² Ω·cm với mật độ vi ống dưới 0,1 cm⁻², đảm bảo rò rỉ tối thiểu cho các thiết bị RF và vi sóng. Vật liệu 3C-N dạng khối, có sẵn ở định dạng 2″ và 4″, cho phép dị epitaxy trên silicon và hỗ trợ các ứng dụng quang tử và MEMS mới. Các tấm wafer SiC loại P 4H/6H-P, được pha tạp nhôm với nồng độ 1×10¹⁶–5×10¹⁸ cm⁻³, tạo điều kiện thuận lợi cho các cấu trúc thiết bị bổ sung.

Các tấm wafer SiC PRIME trải qua quá trình đánh bóng hóa học-cơ học để đạt độ nhám bề mặt RMS <0,2 nm, độ biến thiên tổng độ dày dưới 3 µm và độ cong <10 µm. Các chất nền DUMMY giúp tăng tốc quá trình lắp ráp và kiểm tra đóng gói, trong khi các tấm wafer RESEARCH có độ dày lớp epitaxy từ 2–30 µm và được pha tạp theo yêu cầu. Tất cả các sản phẩm đều được chứng nhận bằng nhiễu xạ tia X (đường cong dao động <30 arcsec) và quang phổ Raman, cùng với các thử nghiệm điện – đo Hall, lập hồ sơ C–V và quét vi ống – đảm bảo tuân thủ tiêu chuẩn JEDEC và SEMI.

Các khối tinh thể có đường kính lên đến 150 mm được nuôi cấy thông qua phương pháp PVT và CVD với mật độ sai lệch dưới 1×10³ cm⁻² và số lượng vi ống thấp. Các tinh thể mầm được cắt trong phạm vi 0,1° so với trục c để đảm bảo quá trình nuôi cấy có thể tái tạo và năng suất cắt lát cao.

Bằng cách kết hợp nhiều loại tinh thể, biến thể pha tạp, cấp chất lượng, kích thước tấm wafer SiC và quy trình sản xuất tinh thể tròn và tinh thể mầm nội bộ, nền tảng chất nền SiC của chúng tôi giúp tối ưu hóa chuỗi cung ứng và đẩy nhanh quá trình phát triển thiết bị cho xe điện, lưới điện thông minh và các ứng dụng trong môi trường khắc nghiệt.

Bảng dữ liệu của tấm wafer SiC loại 4H-N 6 inch

| Bảng dữ liệu tấm wafer SiC 6 inch | ||||

| Tham số | Tham số phụ | Hạng Z | Hạng P | Hạng D |

| Đường kính | 149,5–150,0 mm | 149,5–150,0 mm | 149,5–150,0 mm | |

| Độ dày | 4H-N | 350 µm ± 15 µm | 350 µm ± 25 µm | 350 µm ± 25 µm |

| Độ dày | 4H-SI | 500 µm ± 15 µm | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Định hướng tấm bán dẫn | Lệch trục: 4,0° về phía <11-20> ±0,5° (4H-N); Trên trục: <0001> ±0,5° (4H-SI) | Lệch trục: 4,0° về phía <11-20> ±0,5° (4H-N); Trên trục: <0001> ±0,5° (4H-SI) | Lệch trục: 4,0° về phía <11-20> ±0,5° (4H-N); Trên trục: <0001> ±0,5° (4H-SI) | |

| Mật độ vi ống | 4H-N | ≤ 0,2 cm⁻² | ≤ 2 cm⁻² | ≤ 15 cm⁻² |

| Mật độ vi ống | 4H-SI | ≤ 1 cm⁻² | ≤ 5 cm⁻² | ≤ 15 cm⁻² |

| Điện trở suất | 4H-N | 0,015–0,024 Ω·cm | 0,015–0,028 Ω·cm | 0,015–0,028 Ω·cm |

| Điện trở suất | 4H-SI | ≥ 1×10¹⁰ Ω·cm | ≥ 1×10⁵ Ω·cm | |

| Định hướng phẳng chính | [10-10] ± 5,0° | [10-10] ± 5,0° | [10-10] ± 5,0° | |

| Chiều dài phẳng chính | 4H-N | 47,5 mm ± 2,0 mm | ||

| Chiều dài phẳng chính | 4H-SI | Vết khuyết | ||

| Loại trừ cạnh | 3 mm | |||

| Warp/LTV/TTV/Bow | 2,5 µm / `6 ``m / `25 `` / ``35 `m | 5 µm / 15 µm / 40 µm / ≤60 µm | ||

| Độ nhám | Đánh bóng | Ra ≤ 1 nm | ||

| Độ nhám | CMP | Ra ≤ 0,2 nm | Ra ≤ 0,5 nm | |

| Vết nứt cạnh | Không có | Tổng chiều dài ≤ 20 mm, chiều dài từng đoạn ≤ 2 mm | ||

| Tấm lục giác | Diện tích tích lũy ≤ 0,05% | Diện tích tích lũy ≤ 0,1% | Diện tích tích lũy ≤ 1% | |

| Khu vực đa dạng | Không có | Tổng diện tích tích lũy ≤ 3% | Tổng diện tích tích lũy ≤ 3% | |

| Các tạp chất cacbon | Diện tích tích lũy ≤ 0,05% | Tổng diện tích tích lũy ≤ 3% | ||

| Vết xước trên bề mặt | Không có | Tổng chiều dài ≤ 1 × đường kính tấm wafer | ||

| Mảnh vụn cạnh | Không được phép có chiều rộng và chiều sâu ≥ 0,2 mm. | Tối đa 7 chip, mỗi chip có kích thước ≤ 1 mm. | ||

| TSD (Trật khớp vít ren) | ≤ 500 cm⁻² | Không áp dụng | ||

| BPD (Lệch mặt phẳng đáy) | ≤ 1000 cm⁻² | Không áp dụng | ||

| Ô nhiễm bề mặt | Không có | |||

| Bao bì | Khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer | Khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer | Khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer | |

Bảng dữ liệu của tấm wafer SiC loại 4H-N 4 inch

| Bảng dữ liệu của tấm wafer SiC 4 inch | |||

| Tham số | Sản xuất MPD bằng không | Loại sản xuất tiêu chuẩn (Loại P) | Điểm số giả (Điểm D) |

| Đường kính | 99,5 mm–100,0 mm | ||

| Độ dày (4H-N) | 350 µm ± 15 µm | 350 µm ± 25 µm | |

| Độ dày (4H-Si) | 500 µm ± 15 µm | 500 µm ± 25 µm | |

| Định hướng tấm bán dẫn | Lệch trục: 4,0° về phía <1120> ±0,5° đối với 4H-N; Trên trục: <0001> ±0,5° đối với 4H-Si | ||

| Mật độ vi ống (4H-N) | ≤0,2 cm⁻² | ≤2 cm⁻² | ≤15 cm⁻² |

| Mật độ vi ống (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Điện trở suất (4H-N) | 0,015–0,024 Ω·cm | 0,015–0,028 Ω·cm | |

| Điện trở suất (4H-Si) | ≥1E10 Ω·cm | ≥1E5 Ω·cm | |

| Định hướng phẳng chính | [10-10] ±5,0° | ||

| Chiều dài phẳng chính | 32,5 mm ±2,0 mm | ||

| Chiều dài phẳng thứ cấp | 18,0 mm ±2,0 mm | ||

| Định hướng phẳng thứ cấp | Mặt silicon hướng lên: 90° theo chiều kim đồng hồ so với mặt phẳng chính ±5,0° | ||

| Loại trừ cạnh | 3 mm | ||

| LTV/TTV/Bow Warp | 2,5 µm/<5 µm/<15 µm/<30 µm | ≤10 µm/<15 µm/<25 µm/<40 µm | |

| Độ nhám | Độ nhám bề mặt khi đánh bóng Ra ≤1 nm; Độ nhám bề mặt khi đánh bóng hóa học (CMP) Ra ≤0,2 nm | Ra ≤0,5 nm | |

| Các vết nứt ở cạnh do ánh sáng cường độ cao | Không có | Không có | Tổng chiều dài ≤10 mm; chiều dài từng đoạn ≤2 mm |

| Tấm lục giác bằng ánh sáng cường độ cao | Diện tích tích lũy ≤0,05% | Diện tích tích lũy ≤0,05% | Diện tích tích lũy ≤0,1% |

| Các vùng đa dạng cấu trúc bằng ánh sáng cường độ cao | Không có | Diện tích tích lũy ≤3% | |

| Các tạp chất cacbon có thể nhìn thấy | Diện tích tích lũy ≤0,05% | Diện tích tích lũy ≤3% | |

| Bề mặt silicon bị trầy xước do ánh sáng cường độ cao. | Không có | Tổng chiều dài ≤1 đường kính tấm wafer | |

| Phá hủy các chip cạnh bằng ánh sáng cường độ cao | Không cho phép kích thước có chiều rộng và chiều sâu ≥0,2 mm. | Cho phép 5 cái, mỗi cái ≤1 mm | |

| Sự nhiễm bẩn bề mặt silicon do ánh sáng cường độ cao | Không có | ||

| Trật ren vít | ≤500 cm⁻² | Không áp dụng | |

| Bao bì | Khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer | Khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer | Khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer |

Bảng dữ liệu của tấm wafer SiC loại HPSI 4 inch

| Bảng dữ liệu của tấm wafer SiC loại HPSI 4 inch | |||

| Tham số | Loại sản phẩm đạt chuẩn MPD (Z) | Loại sản xuất tiêu chuẩn (Loại P) | Điểm số giả (Điểm D) |

| Đường kính | 99,5–100,0 mm | ||

| Độ dày (4H-Si) | 500 µm ±20 µm | 500 µm ±25 µm | |

| Định hướng tấm bán dẫn | Lệch trục: 4,0° về phía <11-20> ±0,5° đối với 4H-N; Trên trục: <0001> ±0,5° đối với 4H-Si | ||

| Mật độ vi ống (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Điện trở suất (4H-Si) | ≥1E9 Ω·cm | ≥1E5 Ω·cm | |

| Định hướng phẳng chính | (10-10) ±5,0° | ||

| Chiều dài phẳng chính | 32,5 mm ±2,0 mm | ||

| Chiều dài phẳng thứ cấp | 18,0 mm ±2,0 mm | ||

| Định hướng phẳng thứ cấp | Mặt silicon hướng lên: 90° theo chiều kim đồng hồ so với mặt phẳng chính ±5,0° | ||

| Loại trừ cạnh | 3 mm | ||

| LTV/TTV/Bow Warp | ≤3 µm/<5 µm/<15 µm/<30 µm | ≤10 µm/<15 µm/<25 µm/<40 µm | |

| Độ nhám (mặt C) | Đánh bóng | Ra ≤1 nm | |

| Độ nhám (mặt Si) | CMP | Ra ≤0,2 nm | Ra ≤0,5 nm |

| Các vết nứt ở cạnh do ánh sáng cường độ cao | Không có | Tổng chiều dài ≤10 mm; chiều dài từng đoạn ≤2 mm | |

| Tấm lục giác bằng ánh sáng cường độ cao | Diện tích tích lũy ≤0,05% | Diện tích tích lũy ≤0,05% | Diện tích tích lũy ≤0,1% |

| Các vùng đa dạng cấu trúc bằng ánh sáng cường độ cao | Không có | Diện tích tích lũy ≤3% | |

| Các tạp chất cacbon có thể nhìn thấy | Diện tích tích lũy ≤0,05% | Diện tích tích lũy ≤3% | |

| Bề mặt silicon bị trầy xước do ánh sáng cường độ cao. | Không có | Tổng chiều dài ≤1 đường kính tấm wafer | |

| Phá hủy các chip cạnh bằng ánh sáng cường độ cao | Không cho phép kích thước có chiều rộng và chiều sâu ≥0,2 mm. | Cho phép 5 cái, mỗi cái ≤1 mm | |

| Sự nhiễm bẩn bề mặt silicon do ánh sáng cường độ cao | Không có | Không có | |

| Trật ren vít | ≤500 cm⁻² | Không áp dụng | |

| Bao bì | Khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer | ||

Ứng dụng của tấm wafer SiC

-

Mô-đun nguồn SiC dạng tấm mỏng cho bộ biến tần xe điện

Các MOSFET và diode dựa trên tấm wafer SiC được chế tạo trên chất nền wafer SiC chất lượng cao mang lại tổn hao chuyển mạch cực thấp. Bằng cách tận dụng công nghệ wafer SiC, các mô-đun nguồn này hoạt động ở điện áp và nhiệt độ cao hơn, cho phép tạo ra các bộ biến tần kéo hiệu quả hơn. Việc tích hợp các chip wafer SiC vào các tầng công suất giúp giảm yêu cầu làm mát và kích thước, thể hiện đầy đủ tiềm năng của sự đổi mới wafer SiC. -

Các thiết bị RF tần số cao và 5G trên tấm wafer SiC

Các bộ khuếch đại và công tắc RF được chế tạo trên nền tảng tấm bán dẫn SiC có độ dẫn nhiệt và điện áp đánh thủng vượt trội. Lớp nền tấm SiC giảm thiểu tổn thất điện môi ở tần số GHz, trong khi độ bền vật liệu của tấm SiC cho phép hoạt động ổn định trong điều kiện công suất cao, nhiệt độ cao—điều này làm cho tấm SiC trở thành chất nền được lựa chọn cho các trạm gốc 5G thế hệ tiếp theo và hệ thống radar. -

Các chất nền quang điện tử và LED từ tấm wafer SiC

Đèn LED xanh lam và tia cực tím được chế tạo trên chất nền wafer SiC có ưu điểm là khớp mạng tinh thể tốt và khả năng tản nhiệt tuyệt vời. Việc sử dụng wafer SiC mặt C được đánh bóng đảm bảo các lớp màng mỏng đồng nhất, trong khi độ cứng vốn có của wafer SiC cho phép làm mỏng wafer một cách chính xác và đóng gói thiết bị đáng tin cậy. Điều này làm cho wafer SiC trở thành nền tảng lý tưởng cho các ứng dụng LED công suất cao, tuổi thọ dài.

Hỏi đáp về tấm wafer SiC

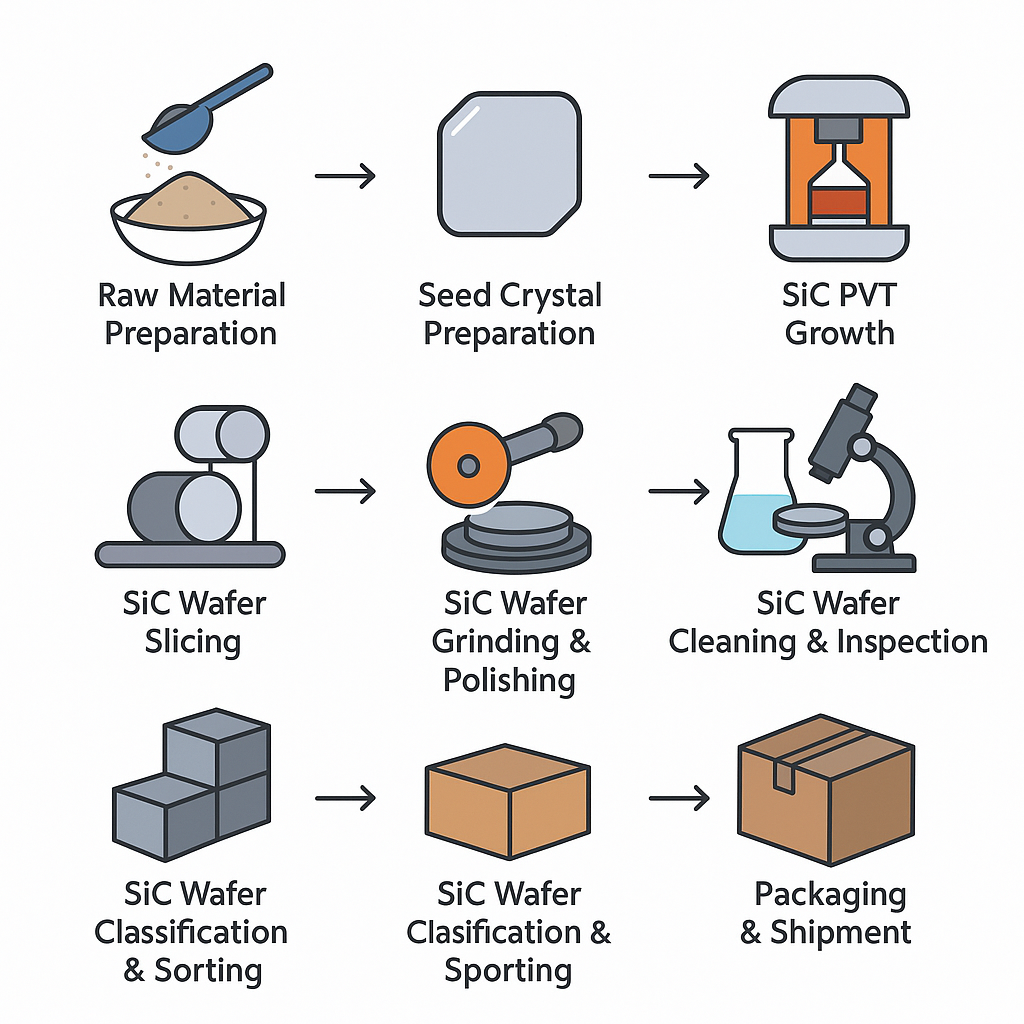

1. Hỏi: Các tấm wafer SiC được sản xuất như thế nào?

MỘT:

Các tấm wafer SiC được sản xuấtCác bước chi tiết

-

Tấm wafer SiCChuẩn bị nguyên liệu thô

- Sử dụng bột SiC loại ≥5N (tạp chất ≤1 ppm).

- Rây và nướng sơ để loại bỏ các hợp chất cacbon hoặc nitơ còn sót lại.

-

SiCChuẩn bị tinh thể mầm

-

Lấy một mảnh tinh thể đơn 4H-SiC, cắt theo hướng 〈0001〉 thành mảnh có kích thước khoảng ~10 × 10 mm².

-

Đánh bóng chính xác đến độ nhám Ra ≤0,1 nm và đánh dấu hướng tinh thể.

-

-

SiCSự phát triển PVT (Vận chuyển hơi vật lý)

-

Chuẩn bị nồi nung than chì: đáy lót bột SiC, đỉnh lót tinh thể mầm.

-

Hút chân không đến áp suất 10⁻³–10⁻⁵ Torr hoặc nạp lại bằng khí heli tinh khiết cao ở áp suất 1 atm.

-

Gia nhiệt vùng nguồn nhiệt đến 2100–2300 ℃, duy trì vùng gieo hạt ở nhiệt độ thấp hơn 100–150 ℃.

-

Kiểm soát tốc độ tăng trưởng ở mức 1–5 mm/h để cân bằng giữa chất lượng và năng suất.

-

-

SiCỦ phôi

-

Ủ phôi SiC vừa được chế tạo ở nhiệt độ 1600–1800 ℃ trong 4–8 giờ.

-

Mục đích: Giảm ứng suất nhiệt và giảm mật độ lệch mạng tinh thể.

-

-

SiCCắt lát bánh wafer

-

Sử dụng cưa dây kim cương để cắt thỏi kim loại thành các lát mỏng có độ dày 0,5–1 mm.

-

Giảm thiểu rung động và lực ngang để tránh nứt vỡ vi mô.

-

-

SiCBánh waferMài và đánh bóng

-

Nghiền thôđể loại bỏ các hư hại do cưa (độ nhám ~10–30 µm).

-

Nghiền mịnđể đạt được độ phẳng ≤5 µm.

-

Đánh bóng cơ học hóa học (CMP)để đạt được bề mặt bóng như gương (Ra ≤0,2 nm).

-

-

SiCBánh waferVệ sinh & Kiểm tra

-

Làm sạch bằng sóng siêu âmtrong dung dịch Piranha (H₂SO₄:H₂O₂), nước DI, sau đó là IPA.

-

Quang phổ XRD/Ramanđể xác nhận kiểu đa hình (4H, 6H, 3C).

-

Giao thoa kếđể đo độ phẳng (<5 µm) và độ cong vênh (<20 µm).

-

Đầu dò bốn điểmđể kiểm tra điện trở suất (ví dụ: HPSI ≥10⁹ Ω·cm).

-

Kiểm tra lỗidưới kính hiển vi ánh sáng phân cực và máy kiểm tra độ xước.

-

-

SiCBánh waferPhân loại và sắp xếp

-

Phân loại các tấm bán dẫn theo loại polytype và loại điện:

-

4H-SiC loại N (4H-N): nồng độ hạt tải điện 10¹⁶–10¹⁸ cm⁻³

-

Vật liệu bán cách điện tinh khiết cao 4H-SiC (4H-HPSI): điện trở suất ≥10⁹ Ω·cm

-

6H-SiC loại N (6H-N)

-

Khác: 3C-SiC, loại P, v.v.

-

-

-

SiCBánh waferĐóng gói & Vận chuyển

2. Câu hỏi: Những ưu điểm chính của tấm wafer SiC so với tấm wafer silicon là gì?

A: So với tấm wafer silicon, tấm wafer SiC cho phép:

-

Hoạt động ở điện áp cao hơn(>1.200 V) với điện trở bật thấp hơn.

-

Độ ổn định nhiệt độ cao hơn(>300 °C) và khả năng quản lý nhiệt được cải thiện.

-

Tốc độ chuyển mạch nhanh hơnVới tổn thất chuyển mạch thấp hơn, giảm thiểu nhu cầu làm mát hệ thống và kích thước của bộ chuyển đổi nguồn.

4. Câu hỏi: Những khuyết tật phổ biến nào ảnh hưởng đến năng suất và hiệu năng của tấm wafer SiC?

A: Các khuyết tật chính trong tấm wafer SiC bao gồm các vi ống, các sai lệch mặt phẳng đáy (BPD) và các vết xước bề mặt. Vi ống có thể gây ra hỏng hóc thiết bị nghiêm trọng; BPD làm tăng điện trở bật theo thời gian; và các vết xước bề mặt dẫn đến vỡ wafer hoặc sự phát triển epitaxy kém. Do đó, việc kiểm tra nghiêm ngặt và giảm thiểu khuyết tật là rất cần thiết để tối đa hóa năng suất wafer SiC.

Thời gian đăng bài: 30/06/2025