Tấm wafer SOI (Silicon-On-Insulator)Đây là một loại vật liệu bán dẫn chuyên dụng với lớp silicon siêu mỏng được hình thành trên một lớp oxit cách điện. Cấu trúc dạng "sandwich" độc đáo này mang lại những cải tiến đáng kể về hiệu năng cho các thiết bị bán dẫn.

Cấu trúc:

Lớp thiết bị (Silicon trên cùng):

Có độ dày từ vài nanomet đến micromet, đóng vai trò là lớp hoạt tính trong quá trình chế tạo transistor.

Lớp oxit chôn vùi (BOX):

Một lớp cách điện silicon dioxide (dày 0,05-15μm) có chức năng cách ly điện lớp thiết bị khỏi chất nền.

Chất nền cơ bản:

Khối silicon (dày 100-500μm) cung cấp sự hỗ trợ cơ học.

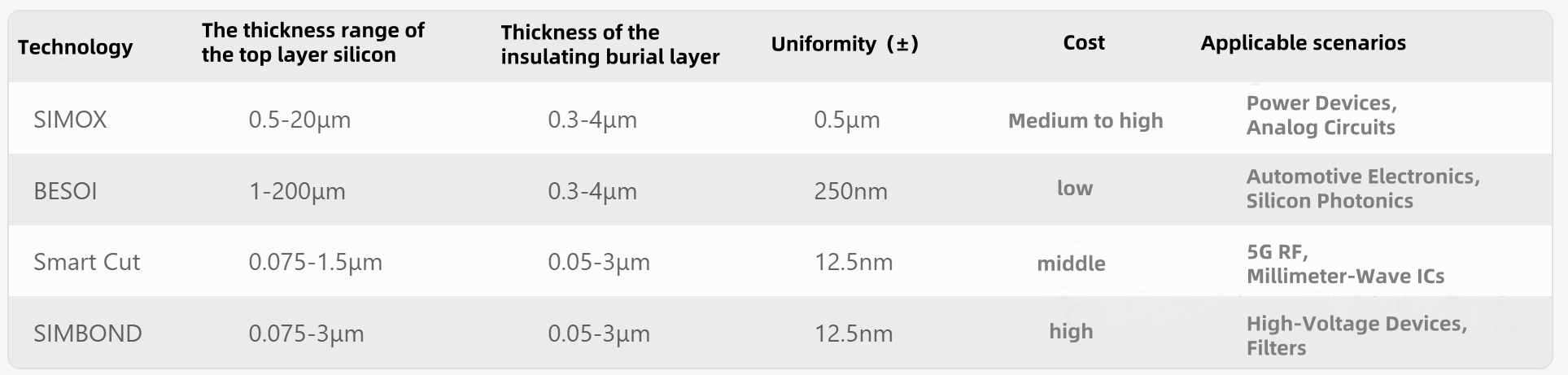

Theo công nghệ quy trình chuẩn bị, các quy trình chính để sản xuất tấm wafer silicon SOI có thể được phân loại như sau: SIMOX (công nghệ cách ly bằng cách bơm oxy), BESOI (công nghệ làm mỏng bằng cách liên kết) và Smart Cut (công nghệ bóc tách thông minh).

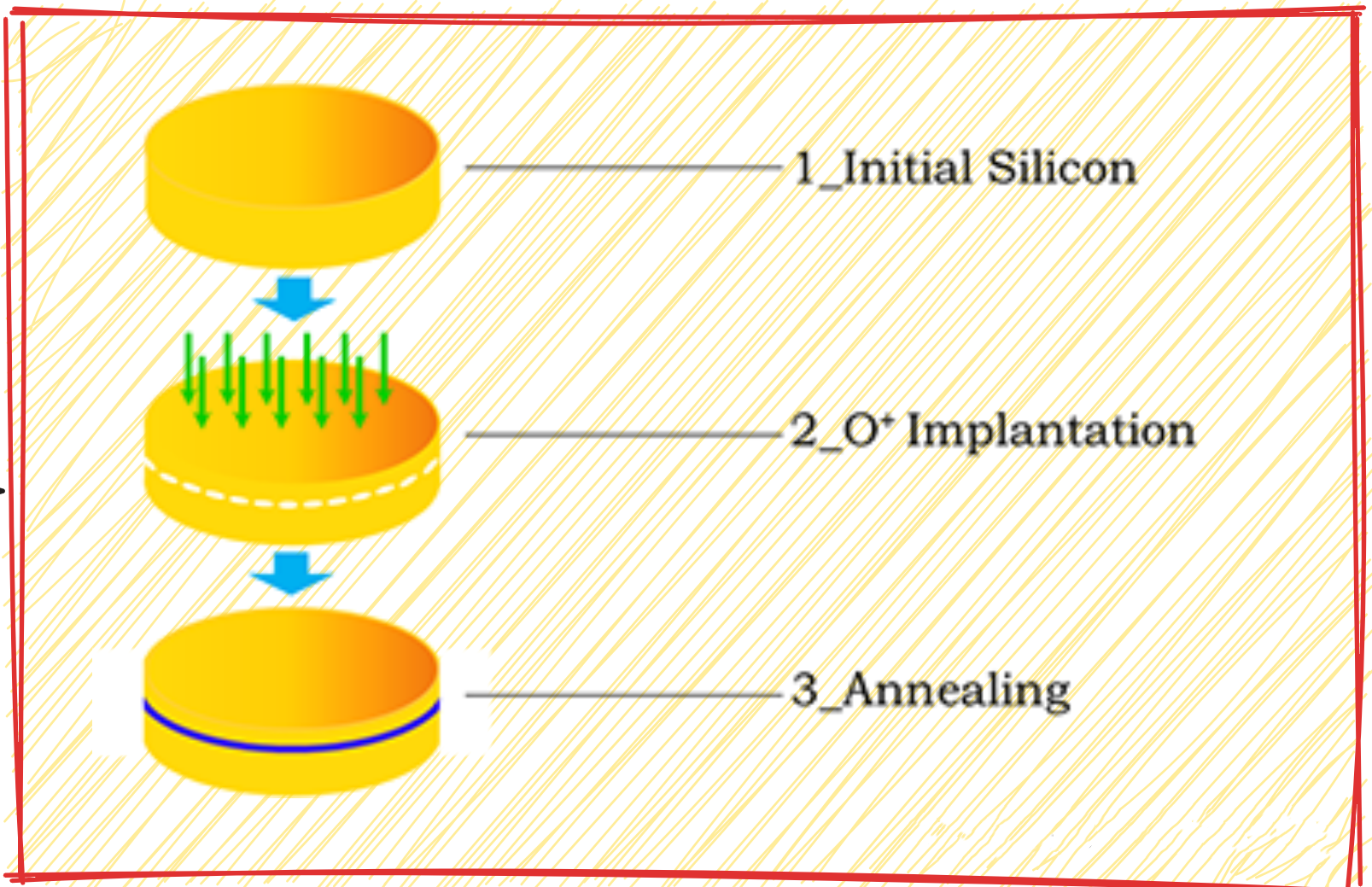

SIMOX (công nghệ cách ly bằng cách tiêm oxy) là một kỹ thuật bao gồm việc tiêm các ion oxy năng lượng cao vào các tấm silicon để tạo thành một lớp silicon dioxide nhúng, sau đó được xử lý bằng phương pháp ủ nhiệt độ cao để sửa chữa các khuyết tật mạng tinh thể. Cốt lõi là tiêm trực tiếp ion oxy để tạo thành lớp oxy nằm sâu bên trong.

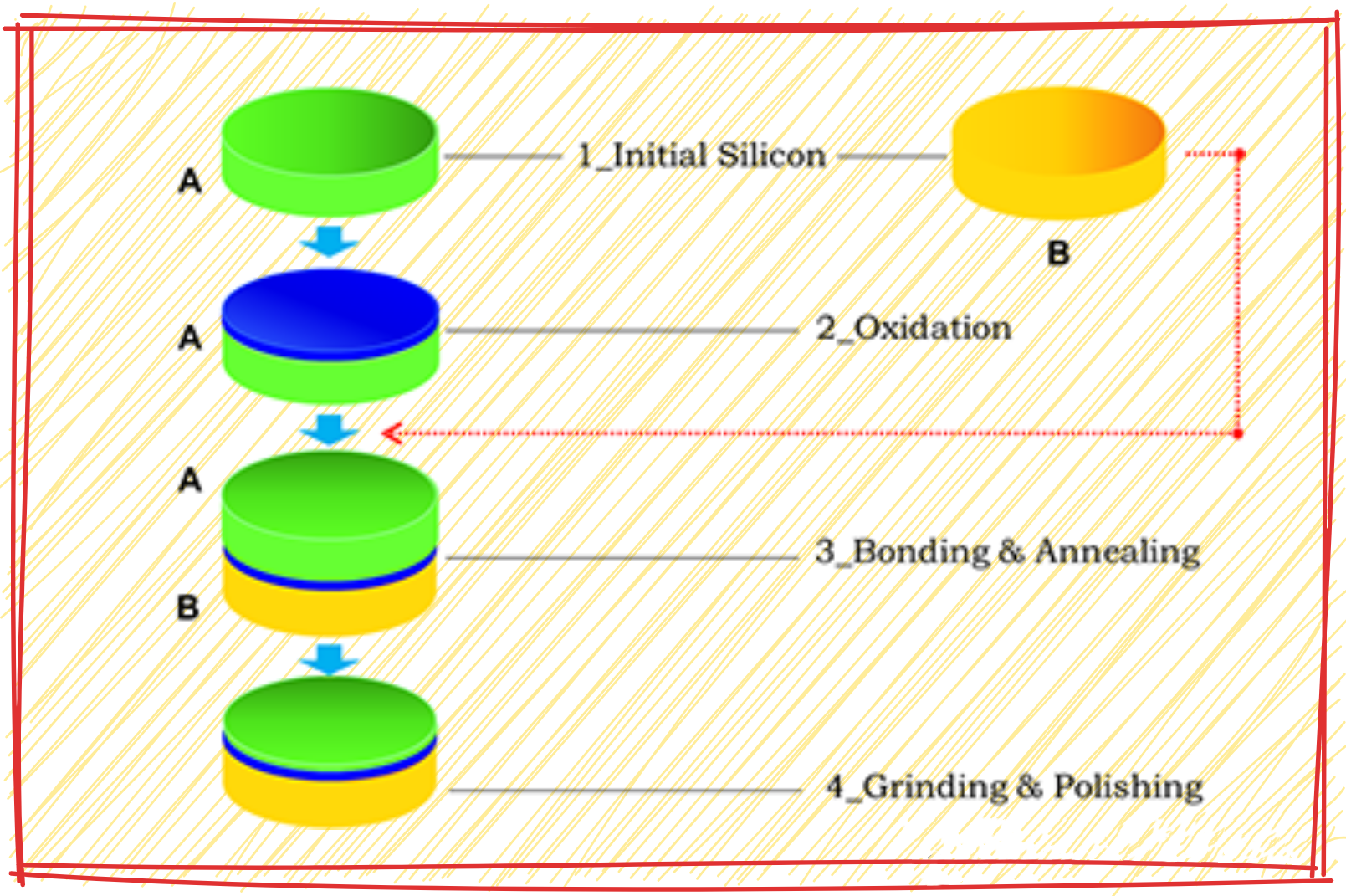

Công nghệ BESOI (Bonding Thinning technology) bao gồm việc liên kết hai tấm silicon và sau đó làm mỏng một trong hai tấm đó bằng phương pháp mài cơ học và khắc hóa học để tạo thành cấu trúc SOI. Cốt lõi nằm ở khâu liên kết và làm mỏng.

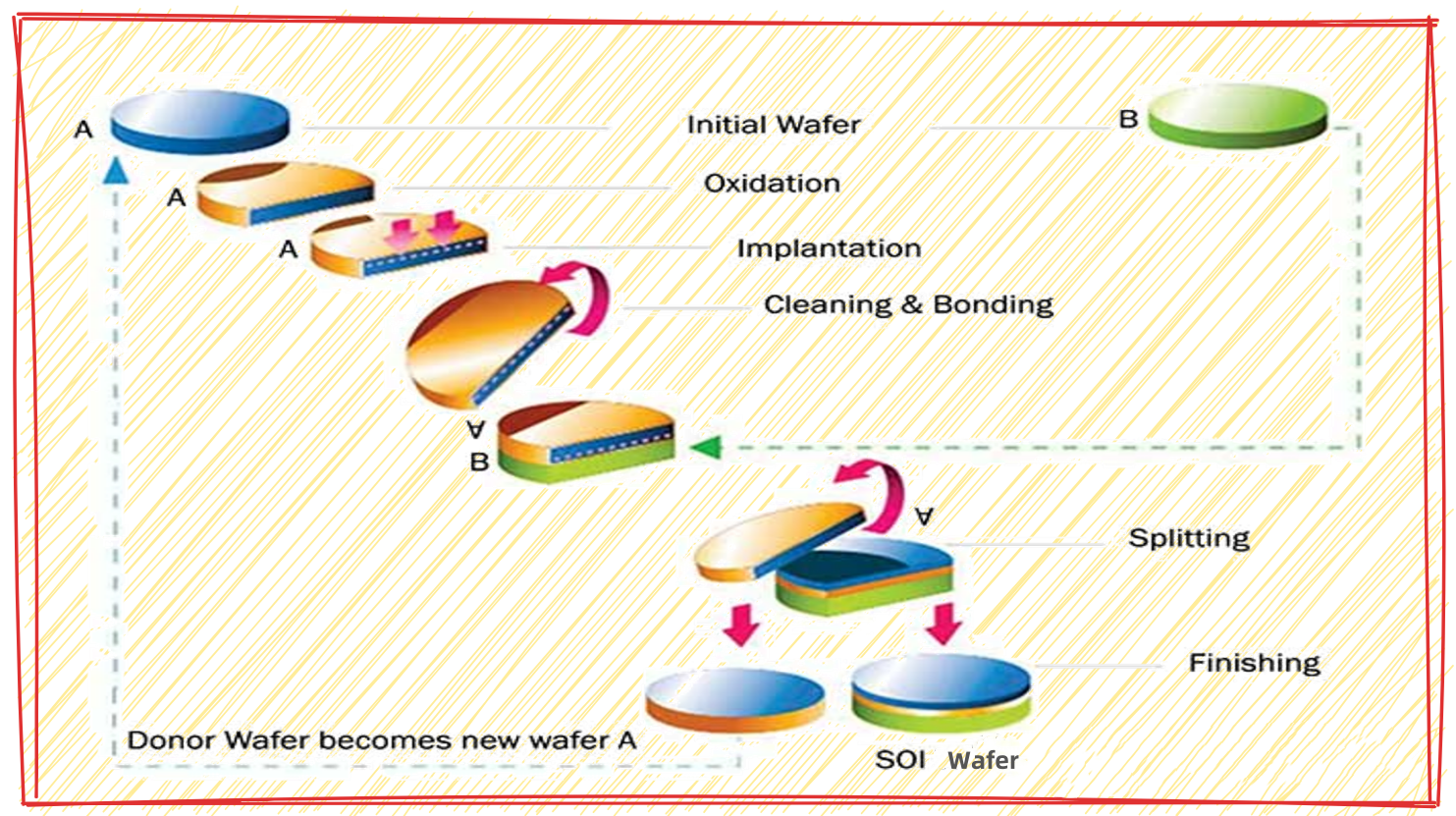

Công nghệ Smart Cut (Công nghệ bóc tách thông minh) tạo ra một lớp bóc tách thông qua việc bơm ion hydro. Sau khi liên kết, quá trình xử lý nhiệt được thực hiện để bóc tách tấm silicon dọc theo lớp ion hydro, tạo thành một lớp silicon siêu mỏng. Cốt lõi của quá trình này là bóc tách bằng cách bơm hydro.

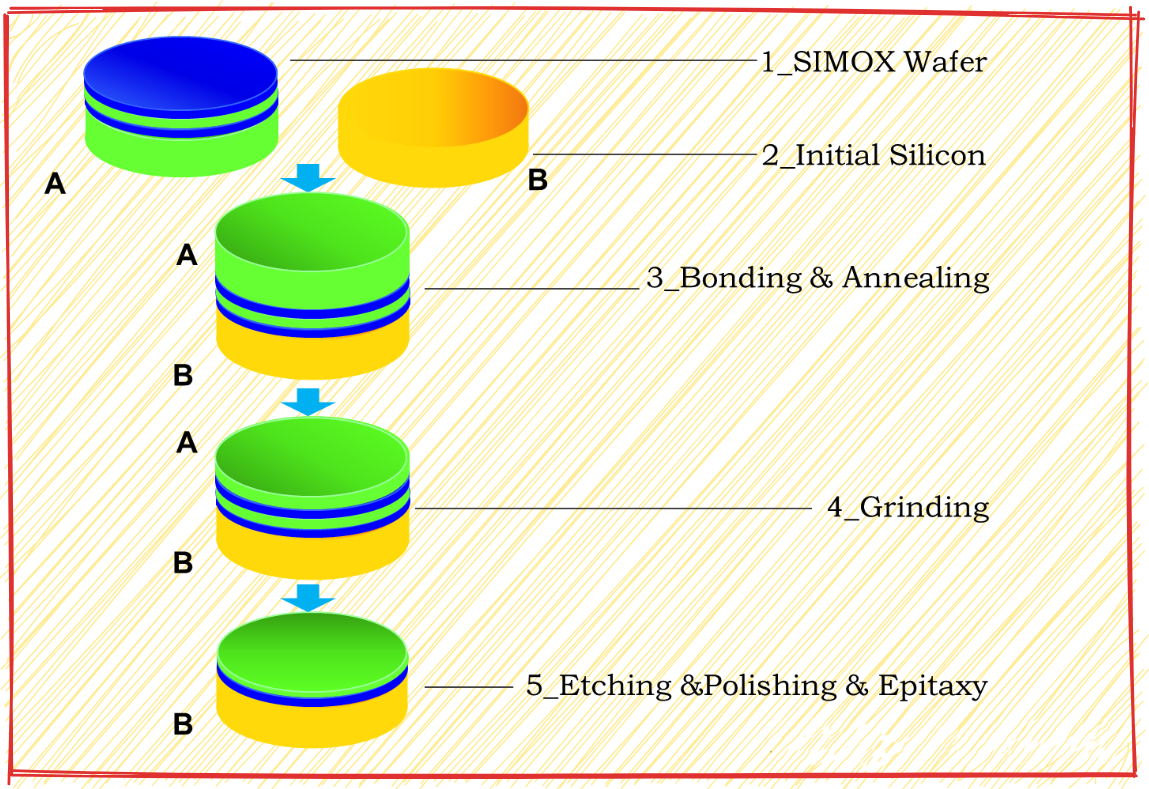

Hiện nay, có một công nghệ khác được gọi là SIMBOND (công nghệ liên kết bằng cách bơm oxy), được phát triển bởi Xinao. Trên thực tế, đây là một phương pháp kết hợp công nghệ cách ly và liên kết bằng cách bơm oxy. Trong phương pháp kỹ thuật này, oxy được bơm vào được sử dụng như một lớp chắn làm mỏng, và lớp oxy nằm sâu bên trong thực tế là một lớp oxy hóa nhiệt. Do đó, nó đồng thời cải thiện các thông số như độ đồng nhất của lớp silicon trên cùng và chất lượng của lớp oxy nằm sâu bên trong.

Các tấm wafer silicon SOI được sản xuất bằng các quy trình kỹ thuật khác nhau có các thông số hiệu năng khác nhau và phù hợp với các kịch bản ứng dụng khác nhau.

Bảng dưới đây tóm tắt những ưu điểm cốt lõi về hiệu năng của tấm wafer silicon SOI, kết hợp với các đặc điểm kỹ thuật và các kịch bản ứng dụng thực tế. So với silicon khối truyền thống, SOI có những ưu điểm vượt trội về sự cân bằng giữa tốc độ và mức tiêu thụ điện năng. (Lưu ý: Hiệu năng của FD-SOI 22nm gần bằng FinFET, nhưng chi phí giảm 30%).

| Lợi thế về hiệu suất | Nguyên lý kỹ thuật | Biểu hiện cụ thể | Các kịch bản ứng dụng điển hình |

| Điện dung ký sinh thấp | Lớp cách điện (BOX) ngăn chặn sự ghép nối điện tích giữa thiết bị và chất nền. | Tốc độ chuyển mạch tăng 15%-30%, mức tiêu thụ điện năng giảm 20%-50%. | Chip truyền thông tần số cao 5G RF |

| Giảm dòng rò rỉ | Lớp cách điện ngăn chặn các đường dẫn dòng điện rò rỉ. | Dòng rò rỉ giảm hơn 90%, kéo dài tuổi thọ pin. | Thiết bị IoT, thiết bị điện tử đeo được |

| Khả năng chống bức xạ được tăng cường | Lớp cách điện ngăn chặn sự tích tụ điện tích do bức xạ gây ra. | Khả năng chịu đựng bức xạ được cải thiện gấp 3-5 lần, giảm các biến cố do sự kiện đơn lẻ gây ra. | Tàu vũ trụ, thiết bị công nghiệp hạt nhân |

| Kiểm soát hiệu ứng kênh ngắn | Lớp silicon mỏng giúp giảm nhiễu điện trường giữa cực thoát và cực nguồn. | Cải thiện độ ổn định điện áp ngưỡng, tối ưu hóa độ dốc dưới ngưỡng. | Các chip logic nút tiên tiến (<14nm) |

| Quản lý nhiệt được cải thiện | Lớp cách nhiệt làm giảm sự truyền nhiệt. | Giảm 30% lượng nhiệt tích tụ, nhiệt độ hoạt động thấp hơn 15-25°C. | Mạch tích hợp 3D, Điện tử ô tô |

| Tối ưu hóa tần số cao | Giảm điện dung ký sinh và tăng cường khả năng di chuyển của hạt tải điện | Độ trễ thấp hơn 20%, hỗ trợ xử lý tín hiệu >30GHz. | Truyền thông mmWave, chip truyền thông vệ tinh |

| Tăng tính linh hoạt trong thiết kế | Không cần dùng chất kích thích, hỗ trợ thiên lệch ngược. | Giảm 13%-20% số bước trong quy trình, mật độ tích hợp cao hơn 40%. | Mạch tích hợp tín hiệu hỗn hợp, Cảm biến |

| Miễn dịch khi khóa cửa | Lớp cách điện ngăn cách các mối nối PN ký sinh. | Ngưỡng dòng điện kích hoạt tăng lên >100mA. | Thiết bị điện cao áp |

Tóm lại, những ưu điểm chính của SOI là: tốc độ xử lý nhanh và tiết kiệm năng lượng hơn.

Nhờ những đặc tính hiệu năng này, SOI có ứng dụng rộng rãi trong các lĩnh vực đòi hỏi hiệu năng tần số và hiệu năng tiêu thụ điện năng xuất sắc.

Như hình dưới đây, dựa trên tỷ lệ các lĩnh vực ứng dụng tương ứng với SOI, có thể thấy rằng các thiết bị RF và thiết bị nguồn chiếm phần lớn thị trường SOI.

| Lĩnh vực ứng dụng | Thị phần |

| RF-SOI (Tần số vô tuyến) | 45% |

| Nguồn SOI | 30% |

| FD-SOI (Đã cạn kiệt hoàn toàn) | 15% |

| SOI quang học | 8% |

| Cảm biến SOI | 2% |

Với sự phát triển của các thị trường như truyền thông di động và xe tự lái, các tấm wafer silicon SOI cũng được kỳ vọng sẽ duy trì tốc độ tăng trưởng nhất định.

XKH, với tư cách là nhà tiên phong hàng đầu trong công nghệ wafer Silicon-On-Insulator (SOI), cung cấp các giải pháp SOI toàn diện từ nghiên cứu và phát triển đến sản xuất hàng loạt bằng cách sử dụng các quy trình sản xuất hàng đầu trong ngành. Danh mục sản phẩm đầy đủ của chúng tôi bao gồm các wafer SOI 200mm/300mm thuộc các biến thể RF-SOI, Power-SOI và FD-SOI, với kiểm soát chất lượng nghiêm ngặt đảm bảo tính nhất quán về hiệu suất vượt trội (độ đồng nhất độ dày trong phạm vi ±1,5%). Chúng tôi cung cấp các giải pháp tùy chỉnh với độ dày lớp oxit chôn (BOX) từ 50nm đến 1,5μm và các thông số điện trở suất khác nhau để đáp ứng các yêu cầu cụ thể. Tận dụng 15 năm kinh nghiệm kỹ thuật và chuỗi cung ứng toàn cầu mạnh mẽ, chúng tôi cung cấp đáng tin cậy các vật liệu nền SOI chất lượng cao cho các nhà sản xuất bán dẫn hàng đầu trên toàn thế giới, cho phép đổi mới chip tiên tiến trong truyền thông 5G, điện tử ô tô và các ứng dụng trí tuệ nhân tạo.

Thời gian đăng bài: 24/04/2025