Công nghệ cắt wafer, một bước quan trọng trong quy trình sản xuất chất bán dẫn, có liên quan trực tiếp đến hiệu suất, năng suất và chi phí sản xuất chip.

#01 Bối cảnh và ý nghĩa của việc cắt wafer

1.1 Định nghĩa về cắt wafer

Cắt wafer (còn được gọi là khắc wafer) là một bước thiết yếu trong sản xuất chất bán dẫn, nhằm mục đích chia các wafer đã qua xử lý thành nhiều đế riêng biệt. Các đế này thường chứa đầy đủ chức năng mạch điện và là thành phần cốt lõi cuối cùng được sử dụng trong sản xuất thiết bị điện tử. Khi thiết kế chip ngày càng phức tạp và kích thước ngày càng thu nhỏ, các yêu cầu về độ chính xác và hiệu quả đối với công nghệ cắt wafer ngày càng khắt khe.

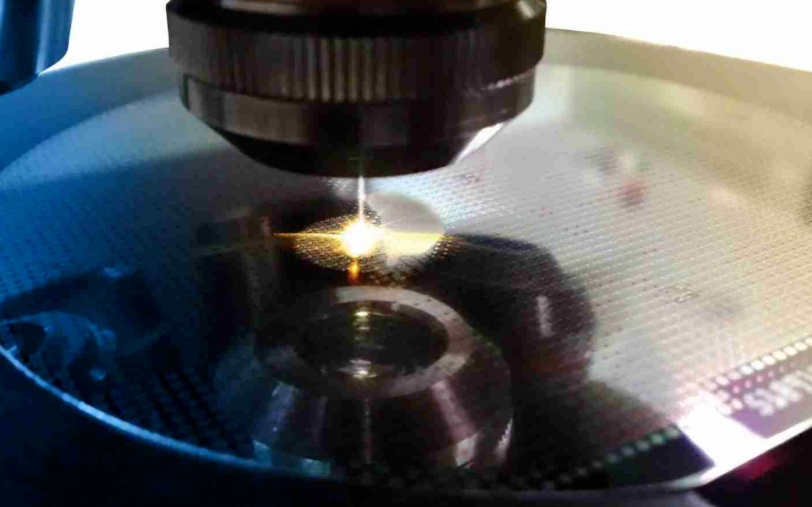

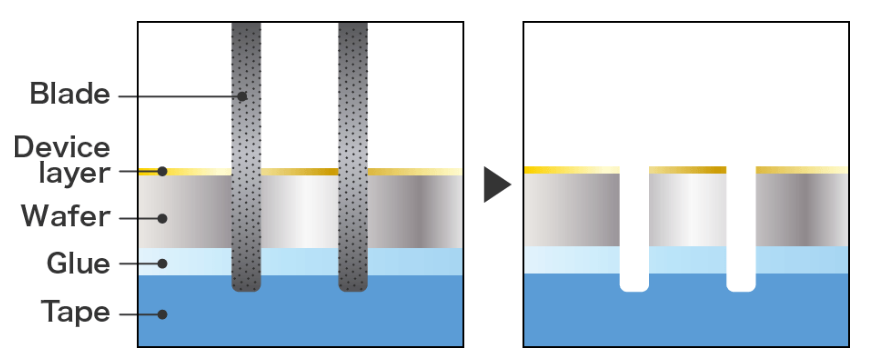

Trong các hoạt động thực tế, cắt wafer thường sử dụng các công cụ có độ chính xác cao như lưỡi cắt kim cương để đảm bảo mỗi khuôn vẫn còn nguyên vẹn và hoạt động đầy đủ. Các bước chính bao gồm chuẩn bị trước khi cắt, kiểm soát chính xác trong quá trình cắt và kiểm tra chất lượng sau khi cắt.

Trước khi cắt, wafer phải được đánh dấu và định vị để đảm bảo đường cắt chính xác. Trong quá trình cắt, các thông số như áp suất và tốc độ của dụng cụ phải được kiểm soát chặt chẽ để tránh làm hỏng wafer. Sau khi cắt, các cuộc kiểm tra chất lượng toàn diện được tiến hành để đảm bảo mỗi chip đều đáp ứng các tiêu chuẩn hiệu suất.

Các nguyên tắc cơ bản của công nghệ cắt wafer không chỉ bao gồm việc lựa chọn thiết bị cắt và thiết lập các thông số quy trình mà còn bao gồm ảnh hưởng của các đặc tính cơ học và đặc điểm của vật liệu đến chất lượng cắt. Ví dụ, wafer silicon điện môi k thấp, do đặc tính cơ học kém, rất dễ bị tập trung ứng suất trong quá trình cắt, dẫn đến các hư hỏng như sứt mẻ và nứt. Độ cứng và độ giòn thấp của vật liệu k thấp khiến chúng dễ bị hư hỏng cấu trúc hơn dưới tác động của lực cơ học hoặc ứng suất nhiệt, đặc biệt là trong quá trình cắt. Sự tiếp xúc giữa dụng cụ và bề mặt wafer, cùng với nhiệt độ cao, có thể làm trầm trọng thêm sự tập trung ứng suất.

Với những tiến bộ trong khoa học vật liệu, công nghệ cắt wafer đã mở rộng ra ngoài các chất bán dẫn gốc silicon truyền thống để bao gồm các vật liệu mới như gali nitride (GaN). Những vật liệu mới này, do độ cứng và đặc tính cấu trúc của chúng, đặt ra những thách thức mới cho quy trình cắt, đòi hỏi phải cải tiến hơn nữa về dụng cụ và kỹ thuật cắt.

Là một quy trình quan trọng trong ngành công nghiệp bán dẫn, việc cắt wafer tiếp tục được tối ưu hóa để đáp ứng nhu cầu ngày càng tăng và những tiến bộ công nghệ, đặt nền tảng cho công nghệ vi điện tử và mạch tích hợp trong tương lai.

Những cải tiến trong công nghệ cắt wafer không chỉ dừng lại ở việc phát triển vật liệu và công cụ phụ trợ mà còn bao gồm tối ưu hóa quy trình, cải tiến hiệu suất thiết bị và kiểm soát chính xác các thông số cắt. Những tiến bộ này nhằm đảm bảo độ chính xác, hiệu quả và tính ổn định cao trong quy trình cắt wafer, đáp ứng nhu cầu của ngành công nghiệp bán dẫn về kích thước nhỏ hơn, tích hợp cao hơn và cấu trúc chip phức tạp hơn.

| Khu vực cải thiện | Các biện pháp cụ thể | Các hiệu ứng |

| Tối ưu hóa quy trình | - Cải thiện khâu chuẩn bị ban đầu, chẳng hạn như định vị wafer và lập kế hoạch đường đi chính xác hơn. | - Giảm lỗi cắt và cải thiện độ ổn định. |

| - Giảm thiểu sai số cắt và tăng cường độ ổn định. | - Áp dụng cơ chế giám sát và phản hồi theo thời gian thực để điều chỉnh áp suất, tốc độ và nhiệt độ của dụng cụ. | |

| - Giảm tỷ lệ vỡ wafer và cải thiện chất lượng chip. | ||

| Nâng cao hiệu suất thiết bị | - Sử dụng hệ thống cơ khí chính xác cao và công nghệ điều khiển tự động tiên tiến. | - Nâng cao độ chính xác khi cắt và giảm thiểu lãng phí vật liệu. |

| - Giới thiệu công nghệ cắt laser phù hợp với vật liệu wafer có độ cứng cao. | - Nâng cao hiệu quả sản xuất và giảm thiểu sai sót thủ công. | |

| - Tăng cường tự động hóa thiết bị để giám sát và điều chỉnh tự động. | ||

| Kiểm soát thông số chính xác | - Điều chỉnh chính xác các thông số như độ sâu cắt, tốc độ, loại dụng cụ và phương pháp làm mát. | - Đảm bảo tính toàn vẹn của khuôn và hiệu suất điện. |

| - Tùy chỉnh các thông số dựa trên vật liệu, độ dày và cấu trúc của wafer. | - Tăng năng suất, giảm lãng phí vật liệu và giảm chi phí sản xuất. | |

| Ý nghĩa chiến lược | - Liên tục khám phá các con đường công nghệ mới, tối ưu hóa quy trình và nâng cao năng lực thiết bị để đáp ứng nhu cầu thị trường. | - Nâng cao năng suất và hiệu suất sản xuất chip, hỗ trợ phát triển vật liệu mới và thiết kế chip tiên tiến. |

1.2 Tầm quan trọng của việc cắt lát wafer

Cắt wafer đóng vai trò quan trọng trong quy trình sản xuất chất bán dẫn, ảnh hưởng trực tiếp đến các bước tiếp theo cũng như chất lượng và hiệu suất của sản phẩm cuối cùng. Tầm quan trọng của nó có thể được mô tả chi tiết như sau:

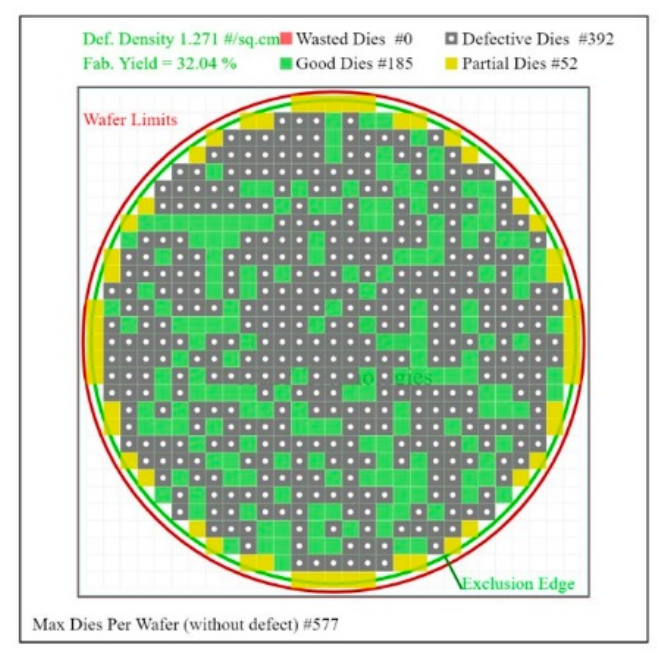

Đầu tiên, độ chính xác và tính nhất quán của quá trình cắt hạt là chìa khóa để đảm bảo năng suất và độ tin cậy của chip. Trong quá trình sản xuất, các tấm wafer trải qua nhiều bước xử lý để tạo thành nhiều cấu trúc mạch phức tạp, đòi hỏi phải được chia chính xác thành từng chip (khuôn). Nếu có sai số đáng kể về căn chỉnh hoặc cắt trong quá trình cắt hạt, các mạch có thể bị hỏng, ảnh hưởng đến chức năng và độ tin cậy của chip. Do đó, công nghệ cắt hạt có độ chính xác cao không chỉ đảm bảo tính toàn vẹn của từng chip mà còn ngăn ngừa hư hỏng các mạch bên trong, cải thiện hiệu suất tổng thể.

Thứ hai, cắt lát wafer có tác động đáng kể đến hiệu quả sản xuất và kiểm soát chi phí. Là một bước quan trọng trong quy trình sản xuất, hiệu quả của nó ảnh hưởng trực tiếp đến tiến độ của các bước tiếp theo. Bằng cách tối ưu hóa quy trình cắt lát, tăng mức độ tự động hóa và cải thiện tốc độ cắt, hiệu quả sản xuất tổng thể có thể được nâng cao đáng kể.

Mặt khác, lãng phí vật liệu trong quá trình cắt hạt lựu là một yếu tố quan trọng trong quản lý chi phí. Việc sử dụng công nghệ cắt hạt lựu tiên tiến không chỉ giảm thiểu tổn thất vật liệu không cần thiết trong quá trình cắt mà còn tăng hiệu suất sử dụng wafer, từ đó giảm chi phí sản xuất.

Với những tiến bộ trong công nghệ bán dẫn, đường kính wafer tiếp tục tăng và mật độ mạch cũng tăng theo, đặt ra yêu cầu cao hơn cho công nghệ cắt hạt. Các wafer lớn hơn đòi hỏi khả năng kiểm soát đường cắt chính xác hơn, đặc biệt là trong các khu vực mạch có mật độ cao, nơi ngay cả những sai lệch nhỏ cũng có thể khiến nhiều chip bị lỗi. Ngoài ra, wafer lớn hơn đòi hỏi nhiều đường cắt hơn và các bước quy trình phức tạp hơn, đòi hỏi phải cải thiện hơn nữa về độ chính xác, tính nhất quán và hiệu quả của công nghệ cắt hạt để đáp ứng những thách thức này.

1.3 Quy trình cắt wafer

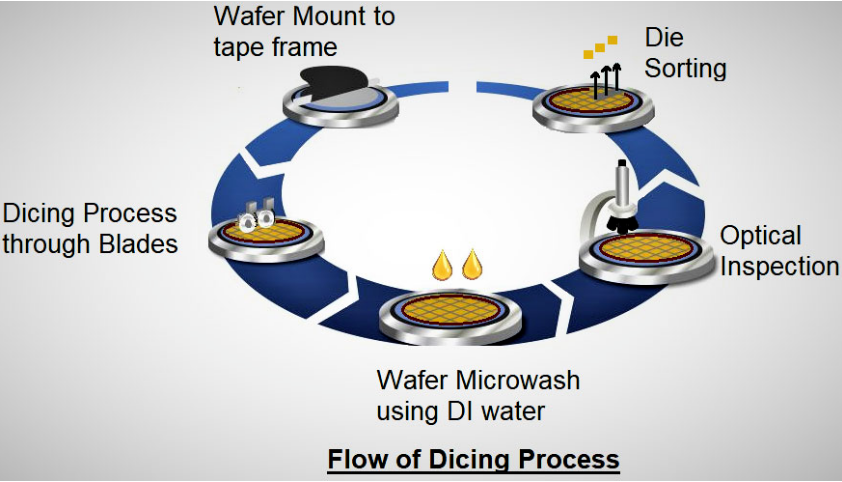

Quy trình cắt lát wafer bao gồm tất cả các bước từ khâu chuẩn bị đến khâu kiểm tra chất lượng cuối cùng, mỗi giai đoạn đều rất quan trọng để đảm bảo chất lượng và hiệu suất của chip cắt lát. Dưới đây là giải thích chi tiết về từng giai đoạn.

| Giai đoạn | Mô tả chi tiết |

| Giai đoạn chuẩn bị | -Vệ sinh wafer:Sử dụng nước có độ tinh khiết cao và các chất tẩy rửa chuyên dụng, kết hợp với phương pháp chà bằng sóng siêu âm hoặc cơ học để loại bỏ tạp chất, hạt và chất gây ô nhiễm, đảm bảo bề mặt sạch sẽ. -Định vị chính xác:Sử dụng thiết bị có độ chính xác cao để đảm bảo wafer được chia chính xác dọc theo đường cắt đã thiết kế. -Cố định wafer: Cố định tấm wafer vào khung băng để duy trì sự ổn định trong quá trình cắt, ngăn ngừa hư hỏng do rung động hoặc chuyển động. |

| Giai đoạn cắt | -Cắt lưỡi dao: Sử dụng lưỡi dao phủ kim cương quay tốc độ cao để cắt vật lý, phù hợp với vật liệu gốc silicon và tiết kiệm chi phí. -Cắt laser:Sử dụng chùm tia laser năng lượng cao để cắt không tiếp xúc, lý tưởng cho các vật liệu giòn hoặc có độ cứng cao như gali nitride, mang lại độ chính xác cao hơn và ít hao hụt vật liệu hơn. -Công nghệ mới: Giới thiệu công nghệ cắt laser và plasma để cải thiện hiệu quả và độ chính xác hơn nữa đồng thời giảm thiểu vùng ảnh hưởng nhiệt. |

| Giai đoạn làm sạch | - Sử dụng nước khử ion (nước DI) và các chất tẩy rửa chuyên dụng, kết hợp với phương pháp làm sạch bằng sóng siêu âm hoặc phun để loại bỏ các mảnh vụn và bụi sinh ra trong quá trình cắt, ngăn ngừa cặn bẩn ảnh hưởng đến các quy trình tiếp theo hoặc hiệu suất điện của chip. - Nước DI có độ tinh khiết cao giúp tránh đưa thêm chất gây ô nhiễm mới, đảm bảo môi trường wafer sạch. |

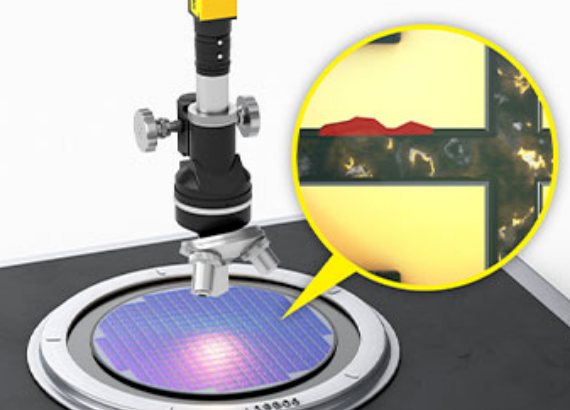

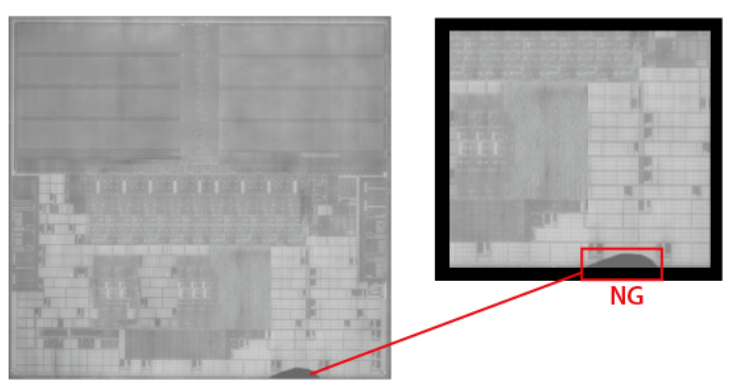

| Giai đoạn kiểm tra | -Kiểm tra quang học:Sử dụng hệ thống phát hiện quang học kết hợp với thuật toán AI để nhanh chóng xác định lỗi, đảm bảo không có vết nứt hoặc sứt mẻ trên các con chip cắt hạt lựu, cải thiện hiệu quả kiểm tra và giảm thiểu lỗi của con người. -Đo lường kích thước: Xác minh rằng kích thước chip đáp ứng thông số kỹ thuật thiết kế. -Kiểm tra hiệu suất điện: Đảm bảo hiệu suất điện của các chip quan trọng đáp ứng các tiêu chuẩn, đảm bảo độ tin cậy trong các ứng dụng tiếp theo. |

| Giai đoạn phân loại | - Sử dụng cánh tay robot hoặc cốc hút chân không để tách các mảnh vụn đạt tiêu chuẩn ra khỏi khung băng và tự động phân loại chúng dựa trên hiệu suất, đảm bảo hiệu quả sản xuất và tính linh hoạt đồng thời cải thiện độ chính xác. |

Quy trình cắt wafer bao gồm làm sạch wafer, định vị, cắt, làm sạch, kiểm tra và phân loại, mỗi bước đều rất quan trọng. Với những tiến bộ trong công nghệ tự động hóa, cắt laser và kiểm tra AI, các hệ thống cắt wafer hiện đại có thể đạt được độ chính xác, tốc độ cao hơn và giảm thiểu tổn thất vật liệu. Trong tương lai, các công nghệ cắt mới như laser và plasma sẽ dần thay thế phương pháp cắt lưỡi dao truyền thống để đáp ứng nhu cầu thiết kế chip ngày càng phức tạp, thúc đẩy hơn nữa sự phát triển của các quy trình sản xuất chất bán dẫn.

Công nghệ cắt wafer và nguyên lý của nó

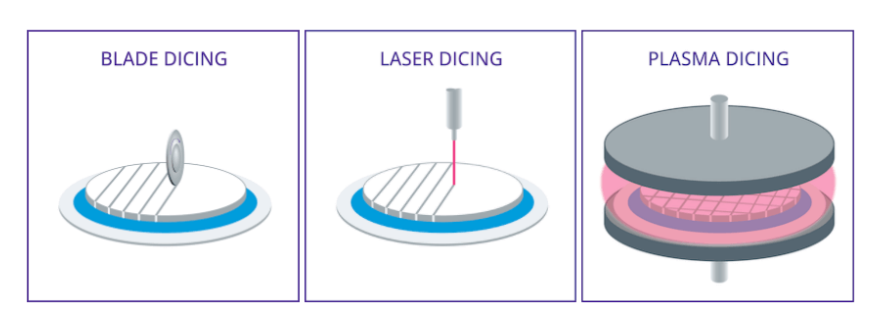

Hình ảnh minh họa ba công nghệ cắt wafer phổ biến:Cắt lưỡi dao,Cắt laser, VàCắt PlasmaDưới đây là phân tích chi tiết và giải thích bổ sung về ba kỹ thuật này:

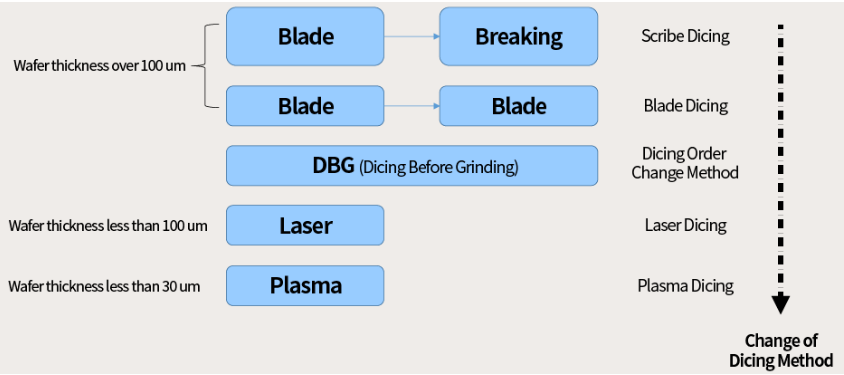

Trong sản xuất bán dẫn, cắt wafer là một bước quan trọng, đòi hỏi phải lựa chọn phương pháp cắt phù hợp dựa trên độ dày của wafer. Bước đầu tiên là xác định độ dày của wafer. Nếu độ dày wafer vượt quá 100 micron, có thể chọn phương pháp cắt bằng dao cắt. Nếu phương pháp cắt bằng dao cắt không phù hợp, có thể sử dụng phương pháp cắt đứt gãy, bao gồm cả kỹ thuật cắt vạch và cắt bằng dao cắt.

Khi độ dày wafer nằm trong khoảng từ 30 đến 100 micron, phương pháp DBG (Cắt hạt trước khi mài) được khuyến nghị. Trong trường hợp này, có thể lựa chọn cắt rãnh, cắt hạt dao hoặc điều chỉnh trình tự cắt tùy theo nhu cầu để đạt được kết quả tốt nhất.

Đối với wafer siêu mỏng có độ dày dưới 30 micron, cắt laser là phương pháp được ưu tiên nhờ khả năng cắt wafer mỏng chính xác mà không gây hư hại quá mức. Nếu cắt laser không đáp ứng được các yêu cầu cụ thể, cắt plasma có thể được sử dụng thay thế. Sơ đồ này cung cấp một lộ trình ra quyết định rõ ràng để đảm bảo lựa chọn công nghệ cắt wafer phù hợp nhất trong các điều kiện độ dày khác nhau.

2.1 Công nghệ cắt cơ khí

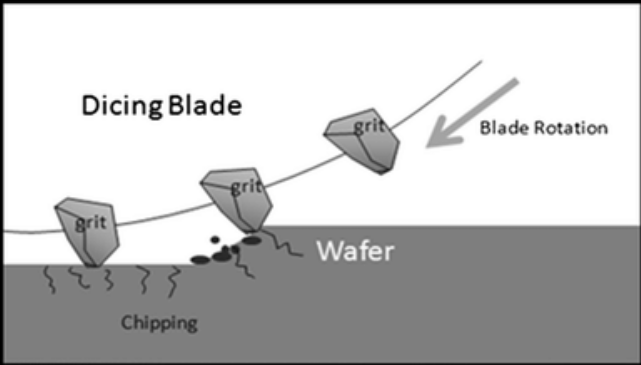

Công nghệ cắt cơ học là phương pháp truyền thống trong cắt lát wafer. Nguyên lý cốt lõi là sử dụng đá mài kim cương quay tốc độ cao làm dụng cụ cắt để cắt lát wafer. Thiết bị chính bao gồm một trục chính ổ trục khí, dẫn động đá mài kim cương ở tốc độ cao để thực hiện cắt hoặc tạo rãnh chính xác theo đường cắt được xác định trước. Công nghệ này được sử dụng rộng rãi trong ngành công nghiệp nhờ chi phí thấp, hiệu quả cao và khả năng ứng dụng rộng rãi.

Thuận lợi

Độ cứng và khả năng chống mài mòn cao của dụng cụ mài kim cương cho phép công nghệ cắt cơ học thích ứng với nhu cầu cắt của nhiều loại vật liệu wafer khác nhau, từ vật liệu silicon truyền thống đến chất bán dẫn hợp chất mới. Vận hành đơn giản, yêu cầu kỹ thuật tương đối thấp, càng thúc đẩy sự phổ biến của phương pháp này trong sản xuất hàng loạt. Ngoài ra, so với các phương pháp cắt khác như cắt laser, cắt cơ học có chi phí kiểm soát tốt hơn, phù hợp với nhu cầu sản xuất số lượng lớn.

Hạn chế

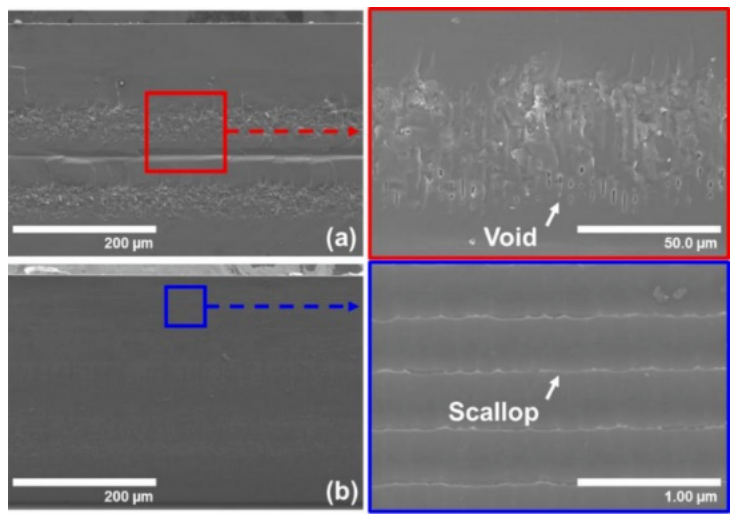

Mặc dù có nhiều ưu điểm, công nghệ cắt cơ học cũng có những hạn chế. Thứ nhất, do tiếp xúc vật lý giữa dụng cụ và wafer, độ chính xác cắt tương đối hạn chế, thường dẫn đến sai lệch kích thước, ảnh hưởng đến độ chính xác của quá trình đóng gói và kiểm tra chip sau này. Thứ hai, các khuyết tật như mẻ và nứt có thể dễ dàng xảy ra trong quá trình cắt cơ học, không chỉ ảnh hưởng đến năng suất mà còn có thể tác động tiêu cực đến độ tin cậy và tuổi thọ của chip. Hư hỏng do ứng suất cơ học đặc biệt bất lợi đối với sản xuất chip mật độ cao, đặc biệt là khi cắt vật liệu giòn, nơi những vấn đề này thường rõ rệt hơn.

Cải tiến công nghệ

Để khắc phục những hạn chế này, các nhà nghiên cứu liên tục tối ưu hóa quy trình cắt cơ học. Những cải tiến chính bao gồm việc nâng cao thiết kế và lựa chọn vật liệu của đá mài để cải thiện độ chính xác và độ bền cắt. Ngoài ra, việc tối ưu hóa thiết kế cấu trúc và hệ thống điều khiển của thiết bị cắt đã cải thiện hơn nữa tính ổn định và tự động hóa của quy trình cắt. Những tiến bộ này giúp giảm thiểu sai sót do thao tác thủ công và cải thiện tính nhất quán của các đường cắt. Việc áp dụng các công nghệ kiểm tra và kiểm soát chất lượng tiên tiến để theo dõi thời gian thực các bất thường trong quá trình cắt cũng đã cải thiện đáng kể độ tin cậy và năng suất cắt.

Phát triển trong tương lai và công nghệ mới

Mặc dù công nghệ cắt cơ học vẫn giữ vị trí quan trọng trong lĩnh vực cắt wafer, các công nghệ cắt mới đang phát triển nhanh chóng cùng với sự phát triển của các quy trình bán dẫn. Ví dụ, việc ứng dụng công nghệ cắt laser nhiệt mang đến những giải pháp mới cho các vấn đề về độ chính xác và khuyết tật trong quá trình cắt cơ học. Phương pháp cắt không tiếp xúc này giúp giảm ứng suất vật lý lên wafer, giảm đáng kể tỷ lệ mẻ và nứt, đặc biệt là khi cắt các vật liệu giòn hơn. Trong tương lai, việc tích hợp công nghệ cắt cơ học với các kỹ thuật cắt mới sẽ mang lại cho ngành sản xuất bán dẫn nhiều lựa chọn và tính linh hoạt hơn, từ đó nâng cao hiệu quả sản xuất và chất lượng chip.

Tóm lại, mặc dù công nghệ cắt cơ học có một số nhược điểm nhất định, nhưng những cải tiến công nghệ liên tục và việc tích hợp với các kỹ thuật cắt mới cho phép công nghệ này vẫn đóng vai trò quan trọng trong sản xuất chất bán dẫn và duy trì khả năng cạnh tranh trong các quy trình tương lai.

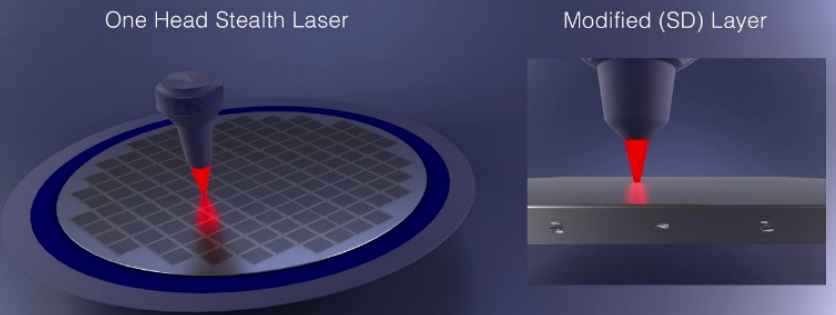

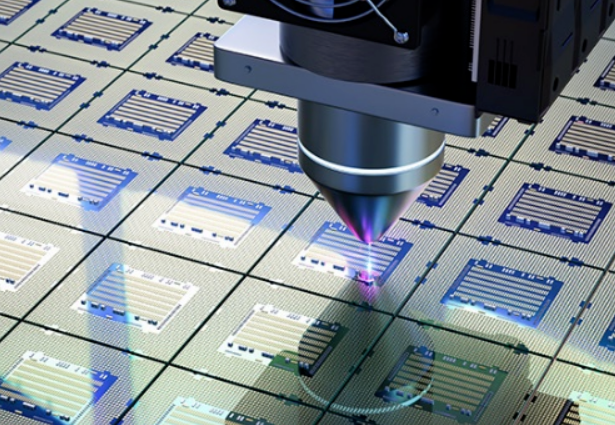

2.2 Công nghệ cắt laser

Công nghệ cắt laser, một phương pháp mới trong cắt wafer, đã dần được chú ý rộng rãi trong ngành công nghiệp bán dẫn nhờ độ chính xác cao, không gây hư hại tiếp xúc cơ học và khả năng cắt nhanh. Công nghệ này sử dụng mật độ năng lượng cao và khả năng hội tụ của chùm tia laser để tạo ra một vùng ảnh hưởng nhiệt nhỏ trên bề mặt vật liệu wafer. Khi chùm tia laser chiếu vào wafer, ứng suất nhiệt sinh ra sẽ làm vật liệu bị gãy tại vị trí được chỉ định, đạt được độ chính xác khi cắt.

Ưu điểm của công nghệ cắt laser

• Độ chính xác cao:Khả năng định vị chính xác của chùm tia laser cho phép cắt chính xác ở cấp độ micron hoặc thậm chí nanomet, đáp ứng các yêu cầu của sản xuất mạch tích hợp hiện đại có mật độ cao, độ chính xác cao.

• Không tiếp xúc cơ học: Cắt laser tránh tiếp xúc vật lý với tấm wafer, ngăn ngừa các vấn đề thường gặp trong quá trình cắt cơ học, chẳng hạn như mẻ và nứt, cải thiện đáng kể tốc độ sản lượng và độ tin cậy của chip.

• Tốc độ cắt nhanh:Tốc độ cắt laser cao góp phần tăng hiệu quả sản xuất, đặc biệt phù hợp với các tình huống sản xuất tốc độ cao, quy mô lớn.

Những thách thức phải đối mặt

• Chi phí thiết bị cao:Đầu tư ban đầu cho thiết bị cắt laser cao, gây áp lực về mặt kinh tế, đặc biệt là đối với các doanh nghiệp sản xuất vừa và nhỏ.

• Kiểm soát quy trình phức tạp:Cắt laser đòi hỏi phải kiểm soát chính xác một số thông số, bao gồm mật độ năng lượng, vị trí tiêu điểm và tốc độ cắt, khiến quá trình này trở nên phức tạp.

• Các vấn đề về vùng bị ảnh hưởng bởi nhiệt: Mặc dù tính chất không tiếp xúc của cắt laser giúp giảm thiểu hư hỏng cơ học, nhưng ứng suất nhiệt do vùng ảnh hưởng nhiệt (HAZ) gây ra có thể ảnh hưởng tiêu cực đến các đặc tính của vật liệu wafer. Cần tối ưu hóa quy trình hơn nữa để giảm thiểu tác động này.

Hướng cải tiến công nghệ

Để giải quyết những thách thức này, các nhà nghiên cứu đang tập trung vào việc giảm chi phí thiết bị, cải thiện hiệu quả cắt và tối ưu hóa quy trình.

• Hệ thống quang học và laser hiệu quả:Bằng cách phát triển các loại laser hiệu quả hơn và hệ thống quang học tiên tiến, có thể giảm chi phí thiết bị đồng thời nâng cao độ chính xác và tốc độ cắt.

• Tối ưu hóa các thông số quy trình:Nghiên cứu chuyên sâu về sự tương tác giữa tia laser và vật liệu wafer đang được tiến hành để cải thiện các quy trình làm giảm vùng ảnh hưởng nhiệt, do đó cải thiện chất lượng cắt.

• Hệ thống điều khiển thông minh:Sự phát triển của công nghệ điều khiển thông minh nhằm mục đích tự động hóa và tối ưu hóa quá trình cắt laser, cải thiện tính ổn định và tính nhất quán của nó.

Công nghệ cắt laser đặc biệt hiệu quả trong các tấm wafer siêu mỏng và các tình huống cắt có độ chính xác cao. Khi kích thước wafer tăng lên và mật độ mạch tăng lên, các phương pháp cắt cơ học truyền thống khó đáp ứng được nhu cầu về độ chính xác và hiệu suất cao của ngành sản xuất bán dẫn hiện đại. Nhờ những ưu điểm độc đáo, cắt laser đang trở thành giải pháp được ưa chuộng trong các lĩnh vực này.

Mặc dù công nghệ cắt laser vẫn còn phải đối mặt với những thách thức như chi phí thiết bị cao và quy trình phức tạp, nhưng những ưu điểm độc đáo về độ chính xác cao và khả năng gây hư hại không tiếp xúc khiến nó trở thành một hướng phát triển quan trọng trong sản xuất bán dẫn. Khi công nghệ laser và hệ thống điều khiển thông minh tiếp tục phát triển, cắt laser được kỳ vọng sẽ cải thiện hơn nữa hiệu suất và chất lượng cắt wafer, thúc đẩy sự phát triển không ngừng của ngành công nghiệp bán dẫn.

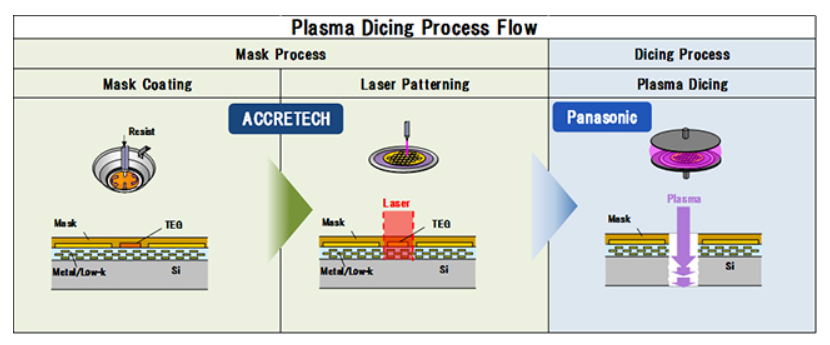

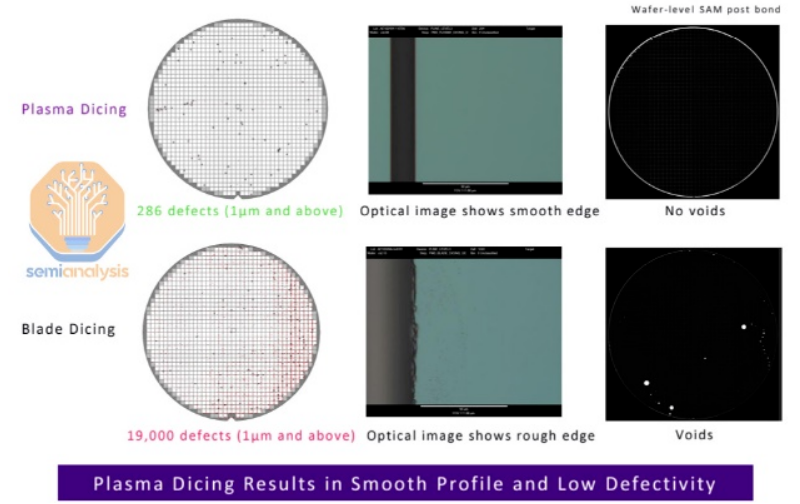

2.3 Công nghệ cắt Plasma

Công nghệ cắt plasma, một phương pháp cắt wafer mới nổi, đã thu hút sự chú ý đáng kể trong những năm gần đây. Công nghệ này sử dụng chùm tia plasma năng lượng cao để cắt wafer một cách chính xác bằng cách kiểm soát năng lượng, tốc độ và đường cắt của chùm tia plasma, đạt được kết quả cắt tối ưu.

Nguyên lý hoạt động và ưu điểm

Quá trình cắt plasma dựa trên chùm tia plasma năng lượng cao, nhiệt độ cao do thiết bị tạo ra. Chùm tia này có thể làm nóng vật liệu wafer đến điểm nóng chảy hoặc bốc hơi trong thời gian rất ngắn, cho phép cắt nhanh chóng. So với cắt cơ học hoặc cắt laser truyền thống, cắt plasma nhanh hơn và tạo ra vùng ảnh hưởng nhiệt nhỏ hơn, giúp giảm thiểu hiệu quả sự xuất hiện của các vết nứt và hư hỏng trong quá trình cắt.

Trong các ứng dụng thực tế, công nghệ cắt plasma đặc biệt hiệu quả trong việc xử lý các wafer có hình dạng phức tạp. Chùm tia plasma năng lượng cao, có thể điều chỉnh của nó có thể dễ dàng cắt các wafer có hình dạng bất thường với độ chính xác cao. Do đó, trong sản xuất vi điện tử, đặc biệt là trong sản xuất chip cao cấp theo yêu cầu và hàng loạt nhỏ, công nghệ này cho thấy triển vọng ứng dụng rộng rãi.

Thách thức và hạn chế

Mặc dù công nghệ cắt plasma có nhiều ưu điểm nhưng nó cũng phải đối mặt với một số thách thức.

• Quá trình phức tạp:Quá trình cắt plasma rất phức tạp và đòi hỏi thiết bị có độ chính xác cao và người vận hành có kinh nghiệm để đảm bảođộ chính xác và ổn định khi cắt.

• Kiểm soát môi trường và an toàn:Bản chất nhiệt độ cao, năng lượng cao của chùm tia plasma đòi hỏi phải kiểm soát môi trường và các biện pháp an toàn nghiêm ngặt, làm tăng tính phức tạp và chi phí triển khai.

Hướng phát triển trong tương lai

Với những tiến bộ công nghệ, những thách thức liên quan đến cắt plasma dự kiến sẽ dần được khắc phục. Bằng cách phát triển thiết bị cắt thông minh hơn và ổn định hơn, sự phụ thuộc vào thao tác thủ công có thể được giảm bớt, từ đó nâng cao hiệu quả sản xuất. Đồng thời, việc tối ưu hóa các thông số quy trình và môi trường cắt sẽ giúp giảm thiểu rủi ro an toàn và chi phí vận hành.

Trong ngành công nghiệp bán dẫn, những đổi mới trong công nghệ cắt và tạo hình wafer đóng vai trò then chốt trong việc thúc đẩy sự phát triển của ngành. Công nghệ cắt plasma, với độ chính xác cao, hiệu quả và khả năng xử lý các hình dạng wafer phức tạp, đã nổi lên như một nhân tố mới đáng kể trong lĩnh vực này. Mặc dù vẫn còn một số thách thức, nhưng những vấn đề này sẽ dần được giải quyết nhờ sự đổi mới công nghệ liên tục, mang lại nhiều khả năng và cơ hội hơn cho ngành sản xuất bán dẫn.

Triển vọng ứng dụng của công nghệ cắt plasma rất rộng lớn và dự kiến sẽ đóng vai trò quan trọng hơn trong sản xuất chất bán dẫn trong tương lai. Thông qua việc liên tục đổi mới và tối ưu hóa công nghệ, cắt plasma không chỉ giải quyết những thách thức hiện tại mà còn trở thành động lực mạnh mẽ cho sự phát triển của ngành công nghiệp bán dẫn.

2.4 Chất lượng cắt và các yếu tố ảnh hưởng

Chất lượng cắt wafer rất quan trọng đối với việc đóng gói chip, thử nghiệm, cũng như hiệu suất và độ tin cậy tổng thể của sản phẩm cuối cùng. Các vấn đề thường gặp trong quá trình cắt bao gồm nứt, mẻ và độ lệch cắt. Những vấn đề này bị ảnh hưởng bởi nhiều yếu tố kết hợp.

| Loại | Nội dung | Sự va chạm |

| Thông số quy trình | Tốc độ cắt, lượng chạy dao và độ sâu cắt ảnh hưởng trực tiếp đến độ ổn định và độ chính xác của quá trình cắt. Cài đặt không đúng có thể dẫn đến tập trung ứng suất và vùng ảnh hưởng nhiệt quá mức, gây ra nứt và mẻ. Việc điều chỉnh các thông số phù hợp dựa trên vật liệu wafer, độ dày và yêu cầu cắt là chìa khóa để đạt được kết quả cắt mong muốn. | Các thông số quy trình phù hợp đảm bảo cắt chính xác và giảm nguy cơ xảy ra khuyết tật như nứt và mẻ. |

| Yếu tố thiết bị và vật liệu | -Chất lượng lưỡi dao: Vật liệu, độ cứng và khả năng chống mài mòn của lưỡi dao ảnh hưởng đến độ mịn của quá trình cắt và độ phẳng của bề mặt cắt. Lưỡi dao kém chất lượng làm tăng ma sát và ứng suất nhiệt, có khả năng dẫn đến nứt hoặc mẻ. Việc lựa chọn vật liệu lưỡi dao phù hợp là rất quan trọng. -Hiệu suất làm mát: Chất làm mát giúp giảm nhiệt độ cắt, giảm thiểu ma sát và làm sạch mảnh vụn. Chất làm mát không hiệu quả có thể dẫn đến nhiệt độ cao và tích tụ mảnh vụn, ảnh hưởng đến chất lượng và hiệu suất cắt. Việc lựa chọn chất làm mát hiệu quả và thân thiện với môi trường là rất quan trọng. | Chất lượng lưỡi dao ảnh hưởng đến độ chính xác và độ mịn của đường cắt. Chất làm mát không hiệu quả có thể dẫn đến chất lượng và hiệu suất cắt kém, do đó cần sử dụng chất làm mát tối ưu. |

| Kiểm soát quy trình và kiểm tra chất lượng | -Kiểm soát quy trình: Theo dõi và điều chỉnh thời gian thực các thông số cắt chính để đảm bảo tính ổn định và nhất quán trong quá trình cắt. -Kiểm tra chất lượng: Kiểm tra ngoại quan sau khi cắt, đo kích thước và thử nghiệm hiệu suất điện giúp xác định và giải quyết kịp thời các vấn đề về chất lượng, cải thiện độ chính xác và tính nhất quán khi cắt. | Kiểm soát quy trình và kiểm tra chất lượng phù hợp giúp đảm bảo kết quả cắt đồng đều, chất lượng cao và phát hiện sớm các vấn đề tiềm ẩn. |

Cải thiện chất lượng cắt

Việc cải thiện chất lượng cắt đòi hỏi một phương pháp tiếp cận toàn diện, xem xét các thông số quy trình, lựa chọn thiết bị và vật liệu, kiểm soát quy trình và kiểm tra. Bằng cách liên tục cải tiến công nghệ cắt và tối ưu hóa phương pháp quy trình, độ chính xác và độ ổn định của quá trình cắt wafer có thể được nâng cao hơn nữa, cung cấp hỗ trợ kỹ thuật đáng tin cậy hơn cho ngành sản xuất bán dẫn.

#03 Xử lý và kiểm tra sau khi cắt

3.1 Vệ sinh và sấy khô

Các bước vệ sinh và sấy khô sau khi cắt wafer rất quan trọng để đảm bảo chất lượng chip và sự vận hành trơn tru của các quy trình tiếp theo. Trong giai đoạn này, việc loại bỏ hoàn toàn các mảnh vụn silicon, cặn chất làm mát và các chất gây ô nhiễm khác phát sinh trong quá trình cắt là rất cần thiết. Điều quan trọng không kém là đảm bảo chip không bị hư hỏng trong quá trình vệ sinh, và sau khi sấy khô, đảm bảo không còn hơi ẩm trên bề mặt chip để ngăn ngừa các vấn đề như ăn mòn hoặc phóng tĩnh điện.

Xử lý sau khi cắt: Quy trình làm sạch và sấy khô

| Bước quy trình | Nội dung | Sự va chạm |

| Quy trình làm sạch | -Phương pháp:Sử dụng chất tẩy rửa chuyên dụng và nước tinh khiết, kết hợp với kỹ thuật chải siêu âm hoặc cơ học để làm sạch. | Đảm bảo loại bỏ hoàn toàn các chất gây ô nhiễm và ngăn ngừa hư hỏng chip trong quá trình vệ sinh. |

| -Lựa chọn chất tẩy rửa: Lựa chọn dựa trên vật liệu wafer và loại chất gây ô nhiễm để đảm bảo làm sạch hiệu quả mà không làm hỏng chip. | Lựa chọn tác nhân phù hợp là chìa khóa để làm sạch và bảo vệ chip hiệu quả. | |

| -Kiểm soát tham số: Kiểm soát chặt chẽ nhiệt độ, thời gian và nồng độ dung dịch vệ sinh để ngăn ngừa các vấn đề về chất lượng do vệ sinh không đúng cách. | Các biện pháp kiểm soát giúp tránh làm hỏng tấm wafer hoặc để lại chất gây ô nhiễm, đảm bảo chất lượng đồng nhất. | |

| Quá trình sấy khô | -Phương pháp truyền thống: Sấy khô tự nhiên và sấy khô bằng không khí nóng có hiệu suất thấp và có thể dẫn đến tích tụ tĩnh điện. | Có thể làm thời gian khô chậm hơn và có thể xảy ra vấn đề tĩnh điện. |

| -Công nghệ hiện đại:Sử dụng các công nghệ tiên tiến như sấy chân không và sấy hồng ngoại để đảm bảo khoai tây chiên khô nhanh và tránh tác hại. | Quá trình sấy nhanh hơn và hiệu quả hơn, giảm nguy cơ phóng tĩnh điện hoặc các vấn đề liên quan đến độ ẩm. | |

| Lựa chọn và bảo trì thiết bị | -Lựa chọn thiết bị:Máy làm sạch và sấy khô hiệu suất cao cải thiện hiệu quả xử lý và kiểm soát chặt chẽ các vấn đề tiềm ẩn trong quá trình xử lý. | Máy móc chất lượng cao đảm bảo xử lý tốt hơn và giảm khả năng xảy ra lỗi trong quá trình vệ sinh và sấy khô. |

| -Bảo trì thiết bị:Kiểm tra và bảo trì thiết bị thường xuyên để đảm bảo thiết bị luôn ở tình trạng hoạt động tối ưu, đảm bảo chất lượng chip. | Bảo trì đúng cách giúp ngăn ngừa hỏng hóc thiết bị, đảm bảo quá trình xử lý đáng tin cậy và chất lượng cao. |

Làm sạch và sấy khô sau khi cắt

Các bước làm sạch và sấy khô sau khi cắt wafer là những quy trình phức tạp và tinh vi, đòi hỏi sự cân nhắc kỹ lưỡng nhiều yếu tố để đảm bảo kết quả xử lý cuối cùng. Bằng cách sử dụng các phương pháp khoa học và quy trình nghiêm ngặt, chúng tôi có thể đảm bảo mỗi con chip bước vào giai đoạn đóng gói và thử nghiệm tiếp theo trong điều kiện tối ưu.

Kiểm tra và thử nghiệm sau khi cắt

| Bước chân | Nội dung | Sự va chạm |

| Bước kiểm tra | 1.Kiểm tra trực quan: Sử dụng thiết bị kiểm tra trực quan hoặc tự động để kiểm tra các khuyết tật nhìn thấy được như vết nứt, mẻ hoặc nhiễm bẩn trên bề mặt chip. Nhanh chóng xác định các chip bị hư hỏng vật lý để tránh lãng phí. | Giúp xác định và loại bỏ các chip lỗi ngay từ đầu quá trình, giảm thiểu thất thoát vật liệu. |

| 2.Đo kích thước: Sử dụng thiết bị đo chính xác để đo chính xác kích thước chip, đảm bảo kích thước cắt đáp ứng thông số kỹ thuật thiết kế và ngăn ngừa các vấn đề về hiệu suất hoặc khó khăn trong đóng gói. | Đảm bảo chip nằm trong giới hạn kích thước yêu cầu, ngăn ngừa tình trạng suy giảm hiệu suất hoặc các vấn đề lắp ráp. | |

| 3.Kiểm tra hiệu suất điện: Đánh giá các thông số điện quan trọng như điện trở, điện dung và độ tự cảm để xác định các chip không đạt tiêu chuẩn và đảm bảo chỉ những chip đạt tiêu chuẩn hiệu suất mới được chuyển sang giai đoạn tiếp theo. | Đảm bảo chỉ những chip có chức năng và hiệu suất đã được kiểm tra mới được tiếp tục trong quy trình, giảm thiểu nguy cơ hỏng hóc ở các giai đoạn sau. | |

| Bước thử nghiệm | 1.Kiểm tra chức năng: Xác minh chức năng cơ bản của chip hoạt động như mong đợi, xác định và loại bỏ các chip có bất thường về chức năng. | Đảm bảo chip đáp ứng các yêu cầu hoạt động cơ bản trước khi chuyển sang các giai đoạn sau. |

| 2.Kiểm tra độ tin cậy: Đánh giá độ ổn định hiệu suất của chip khi sử dụng trong thời gian dài hoặc trong môi trường khắc nghiệt, thường bao gồm thử nghiệm lão hóa ở nhiệt độ cao, thử nghiệm ở nhiệt độ thấp và thử nghiệm độ ẩm để mô phỏng các điều kiện khắc nghiệt trong thế giới thực. | Đảm bảo chip có thể hoạt động đáng tin cậy trong nhiều điều kiện môi trường khác nhau, cải thiện độ bền và tính ổn định của sản phẩm. | |

| 3.Kiểm tra khả năng tương thích: Xác minh rằng chip hoạt động bình thường với các thành phần hoặc hệ thống khác, đảm bảo không có lỗi hoặc hiệu suất giảm do không tương thích. | Đảm bảo hoạt động trơn tru trong các ứng dụng thực tế bằng cách ngăn ngừa các vấn đề về khả năng tương thích. |

3.3 Đóng gói và bảo quản

Sau khi cắt wafer, chip là sản phẩm đầu ra quan trọng của quy trình sản xuất chất bán dẫn, và các công đoạn đóng gói và lưu trữ cũng quan trọng không kém. Các biện pháp đóng gói và lưu trữ phù hợp không chỉ cần thiết để đảm bảo an toàn và ổn định cho chip trong quá trình vận chuyển và lưu trữ mà còn hỗ trợ mạnh mẽ cho các công đoạn sản xuất, thử nghiệm và đóng gói tiếp theo.

Tóm tắt các giai đoạn kiểm tra và thử nghiệm:

Các bước kiểm tra và thử nghiệm chip sau khi cắt wafer bao gồm nhiều khía cạnh, bao gồm kiểm tra trực quan, đo kích thước, kiểm tra hiệu suất điện, kiểm tra chức năng, kiểm tra độ tin cậy và kiểm tra khả năng tương thích. Các bước này được kết nối và bổ sung cho nhau, tạo thành một rào cản vững chắc để đảm bảo chất lượng và độ tin cậy của sản phẩm. Thông qua các quy trình kiểm tra và thử nghiệm nghiêm ngặt, các vấn đề tiềm ẩn có thể được xác định và giải quyết kịp thời, đảm bảo sản phẩm cuối cùng đáp ứng yêu cầu và kỳ vọng của khách hàng.

| Diện mạo | Nội dung |

| Biện pháp đóng gói | 1.Chống tĩnh điện:Vật liệu đóng gói phải có khả năng chống tĩnh điện tuyệt vời để ngăn ngừa tĩnh điện làm hỏng thiết bị hoặc ảnh hưởng đến hiệu suất của chúng. |

| 2.Chống ẩm:Vật liệu đóng gói phải có khả năng chống ẩm tốt để ngăn ngừa sự ăn mòn và suy giảm hiệu suất điện do độ ẩm gây ra. | |

| 3.Chống sốc:Vật liệu đóng gói phải có khả năng hấp thụ sốc hiệu quả để bảo vệ các con chip khỏi rung động và va đập trong quá trình vận chuyển. | |

| Môi trường lưu trữ | 1.Kiểm soát độ ẩm: Kiểm soát chặt chẽ độ ẩm trong phạm vi thích hợp để ngăn ngừa sự hấp thụ độ ẩm và ăn mòn do độ ẩm quá cao hoặc các vấn đề tĩnh điện do độ ẩm thấp. |

| 2.Sự sạch sẽ: Duy trì môi trường lưu trữ sạch sẽ để tránh bụi và tạp chất làm nhiễm bẩn chip. | |

| 3.Kiểm soát nhiệt độ: Đặt phạm vi nhiệt độ hợp lý và duy trì sự ổn định nhiệt độ để ngăn ngừa hiện tượng lão hóa nhanh do nhiệt độ quá cao hoặc các vấn đề ngưng tụ do nhiệt độ thấp gây ra. | |

| Kiểm tra thường xuyên | Thường xuyên kiểm tra và đánh giá chip lưu trữ bằng cách kiểm tra trực quan, đo kích thước và thử nghiệm hiệu suất điện để xác định và xử lý kịp thời các vấn đề tiềm ẩn. Dựa trên thời gian và điều kiện lưu trữ, hãy lập kế hoạch sử dụng chip để đảm bảo chúng được sử dụng trong điều kiện tối ưu. |

Vấn đề về các vết nứt nhỏ và hư hỏng trong quá trình cắt wafer là một thách thức đáng kể trong sản xuất chất bán dẫn. Ứng suất cắt là nguyên nhân chính gây ra hiện tượng này, vì nó tạo ra các vết nứt nhỏ và hư hỏng trên bề mặt wafer, dẫn đến tăng chi phí sản xuất và giảm chất lượng sản phẩm.

Để giải quyết thách thức này, điều quan trọng là phải giảm thiểu ứng suất cắt và áp dụng các kỹ thuật, công cụ và điều kiện cắt tối ưu. Việc chú ý cẩn thận đến các yếu tố như vật liệu lưỡi cắt, tốc độ cắt, áp suất và phương pháp làm mát có thể giúp giảm sự hình thành các vết nứt nhỏ và cải thiện năng suất tổng thể của quy trình. Ngoài ra, các nghiên cứu đang được tiến hành về các công nghệ cắt tiên tiến hơn, chẳng hạn như cắt laser, đang tìm cách giảm thiểu hơn nữa những vấn đề này.

Là vật liệu dễ vỡ, wafer dễ bị thay đổi cấu trúc bên trong khi chịu ứng suất cơ học, nhiệt hoặc hóa học, dẫn đến hình thành các vết nứt nhỏ. Mặc dù những vết nứt này có thể không dễ nhận thấy ngay lập tức, nhưng chúng có thể lan rộng và gây ra thiệt hại nghiêm trọng hơn trong quá trình sản xuất. Vấn đề này trở nên đặc biệt nghiêm trọng trong các giai đoạn đóng gói và thử nghiệm tiếp theo, khi nhiệt độ dao động và ứng suất cơ học bổ sung có thể khiến các vết nứt nhỏ này phát triển thành các vết nứt có thể nhìn thấy được, có khả năng dẫn đến hỏng chip.

Để giảm thiểu rủi ro này, điều cần thiết là kiểm soát quá trình cắt cẩn thận bằng cách tối ưu hóa các thông số như tốc độ cắt, áp suất và nhiệt độ. Sử dụng các phương pháp cắt ít gây tổn thương hơn, chẳng hạn như cắt laser, có thể giảm ứng suất cơ học lên wafer và giảm thiểu sự hình thành các vết nứt nhỏ. Ngoài ra, việc áp dụng các phương pháp kiểm tra tiên tiến như quét hồng ngoại hoặc chụp X-quang trong quá trình cắt wafer có thể giúp phát hiện các vết nứt ở giai đoạn đầu trước khi chúng gây ra thiệt hại nghiêm trọng hơn.

Hư hỏng bề mặt wafer là một mối quan tâm đáng kể trong quá trình cắt, vì nó có thể ảnh hưởng trực tiếp đến hiệu suất và độ tin cậy của chip. Những hư hỏng này có thể do sử dụng dụng cụ cắt không đúng cách, thông số cắt không chính xác hoặc các khuyết tật vật liệu vốn có trong chính wafer. Bất kể nguyên nhân là gì, những hư hỏng này đều có thể dẫn đến thay đổi điện trở hoặc điện dung của mạch, ảnh hưởng đến hiệu suất tổng thể.

Để giải quyết những vấn đề này, hai chiến lược chính đang được nghiên cứu:

1. Tối ưu hóa các thông số và dụng cụ cắt:Bằng cách sử dụng lưỡi dao sắc hơn, điều chỉnh tốc độ cắt và thay đổi độ sâu cắt, có thể giảm thiểu sự tập trung ứng suất trong quá trình cắt, do đó giảm khả năng hư hỏng.

2. Khám phá công nghệ cắt mới: Các kỹ thuật tiên tiến như cắt laser và cắt plasma mang lại độ chính xác cao hơn, đồng thời có khả năng giảm thiểu mức độ hư hỏng trên wafer. Các công nghệ này đang được nghiên cứu để tìm ra cách đạt được độ chính xác cắt cao đồng thời giảm thiểu ứng suất nhiệt và cơ học trên wafer.

Diện tích tác động nhiệt và ảnh hưởng của nó đến hiệu suất

Trong các quy trình cắt nhiệt như cắt laser và plasma, nhiệt độ cao chắc chắn sẽ tạo ra một vùng va chạm nhiệt trên bề mặt wafer. Vùng này, nơi có độ dốc nhiệt độ đáng kể, có thể làm thay đổi các đặc tính của vật liệu, ảnh hưởng đến hiệu suất cuối cùng của chip.

Tác động của Vùng ảnh hưởng nhiệt (TAZ):

Sự thay đổi cấu trúc tinh thể: Dưới nhiệt độ cao, các nguyên tử bên trong vật liệu wafer có thể sắp xếp lại, gây ra sự biến dạng trong cấu trúc tinh thể. Sự biến dạng này làm suy yếu vật liệu, giảm độ bền cơ học và độ ổn định, làm tăng nguy cơ hỏng chip trong quá trình sử dụng.

Những thay đổi về tính chất điện: Nhiệt độ cao có thể làm thay đổi nồng độ hạt tải điện và độ linh động trong vật liệu bán dẫn, ảnh hưởng đến độ dẫn điện và hiệu suất truyền tải dòng điện của chip. Những thay đổi này có thể làm giảm hiệu suất chip, khiến chip không còn phù hợp với mục đích sử dụng ban đầu.

Để giảm thiểu những tác động này, việc kiểm soát nhiệt độ trong quá trình cắt, tối ưu hóa các thông số cắt và khám phá các phương pháp như tia làm mát hoặc xử lý sau xử lý là những chiến lược thiết yếu để giảm mức độ tác động nhiệt và duy trì tính toàn vẹn của vật liệu.

Nhìn chung, cả vết nứt vi mô và vùng va chạm nhiệt đều là những thách thức quan trọng trong công nghệ cắt wafer. Việc tiếp tục nghiên cứu, cùng với những tiến bộ công nghệ và các biện pháp kiểm soát chất lượng, sẽ là cần thiết để cải thiện chất lượng sản phẩm bán dẫn và nâng cao khả năng cạnh tranh trên thị trường.

Các biện pháp kiểm soát vùng tác động nhiệt:

Tối ưu hóa các thông số quy trình cắt: Việc giảm tốc độ cắt và công suất cắt có thể giảm thiểu hiệu quả kích thước của vùng va chạm nhiệt (TAZ). Điều này giúp kiểm soát lượng nhiệt sinh ra trong quá trình cắt, ảnh hưởng trực tiếp đến các đặc tính vật liệu của wafer.

Công nghệ làm mát tiên tiến: Việc áp dụng các công nghệ như làm mát bằng nitơ lỏng và làm mát bằng vi lưu chất có thể hạn chế đáng kể phạm vi vùng tác động nhiệt. Các phương pháp làm mát này giúp tản nhiệt hiệu quả hơn, do đó bảo toàn các đặc tính vật liệu của wafer và giảm thiểu hư hỏng do nhiệt.

Lựa chọn vật liệu: Các nhà nghiên cứu đang khám phá các vật liệu mới, chẳng hạn như ống nano carbon và graphene, sở hữu độ dẫn nhiệt và độ bền cơ học tuyệt vời. Những vật liệu này có thể giảm vùng va chạm nhiệt đồng thời cải thiện hiệu suất tổng thể của chip.

Tóm lại, mặc dù vùng va chạm nhiệt là hệ quả tất yếu của công nghệ cắt nhiệt, nhưng nó có thể được kiểm soát hiệu quả thông qua các kỹ thuật xử lý tối ưu và lựa chọn vật liệu. Nghiên cứu trong tương lai có thể sẽ tập trung vào việc tinh chỉnh và tự động hóa các quy trình cắt nhiệt để đạt được hiệu quả và độ chính xác cao hơn trong việc cắt wafer.

Chiến lược cân bằng:

Việc đạt được sự cân bằng tối ưu giữa năng suất wafer và hiệu quả sản xuất là một thách thức liên tục trong công nghệ cắt wafer. Các nhà sản xuất cần xem xét nhiều yếu tố, chẳng hạn như nhu cầu thị trường, chi phí sản xuất và chất lượng sản phẩm, để phát triển chiến lược sản xuất và các thông số quy trình hợp lý. Đồng thời, việc áp dụng thiết bị cắt tiên tiến, cải thiện kỹ năng vận hành và tăng cường kiểm soát chất lượng nguyên liệu thô là điều cần thiết để duy trì hoặc thậm chí cải thiện năng suất đồng thời tăng hiệu quả sản xuất.

Những thách thức và cơ hội trong tương lai:

Với sự tiến bộ của công nghệ bán dẫn, việc cắt wafer đang đối mặt với những thách thức và cơ hội mới. Khi kích thước chip thu nhỏ và độ tích hợp tăng lên, yêu cầu về độ chính xác và chất lượng cắt cũng tăng lên đáng kể. Đồng thời, các công nghệ mới nổi cũng mang đến những ý tưởng mới cho việc phát triển kỹ thuật cắt wafer. Các nhà sản xuất phải luôn theo kịp động lực thị trường và xu hướng công nghệ, liên tục điều chỉnh và tối ưu hóa chiến lược sản xuất và thông số quy trình để đáp ứng những thay đổi của thị trường và nhu cầu công nghệ.

Tóm lại, bằng cách kết hợp các yếu tố về nhu cầu thị trường, chi phí sản xuất và chất lượng sản phẩm, đồng thời giới thiệu thiết bị và công nghệ tiên tiến, nâng cao kỹ năng vận hành và tăng cường kiểm soát nguyên liệu thô, các nhà sản xuất có thể đạt được sự cân bằng tốt nhất giữa năng suất wafer và hiệu quả sản xuất trong quá trình cắt wafer, dẫn đến sản xuất sản phẩm bán dẫn hiệu quả và chất lượng cao.

Triển vọng tương lai:

Với những tiến bộ công nghệ nhanh chóng, công nghệ bán dẫn đang phát triển với tốc độ chưa từng có. Là một bước tiến quan trọng trong sản xuất bán dẫn, công nghệ cắt wafer đang sẵn sàng cho những bước phát triển mới đầy thú vị. Nhìn về tương lai, công nghệ cắt wafer được kỳ vọng sẽ đạt được những cải tiến đáng kể về độ chính xác, hiệu suất và chi phí, thổi luồng sinh khí mới vào sự tăng trưởng liên tục của ngành công nghiệp bán dẫn.

Tăng độ chính xác:

Trong hành trình theo đuổi độ chính xác cao hơn, công nghệ cắt wafer sẽ liên tục vượt qua giới hạn của các quy trình hiện có. Bằng cách nghiên cứu sâu sắc các cơ chế vật lý và hóa học của quá trình cắt và kiểm soát chính xác các thông số cắt, kết quả cắt sẽ tinh xảo hơn, đáp ứng các yêu cầu thiết kế mạch ngày càng phức tạp. Ngoài ra, việc khám phá các vật liệu và phương pháp cắt mới sẽ cải thiện đáng kể năng suất và chất lượng.

Nâng cao hiệu quả:

Thiết bị cắt wafer mới sẽ tập trung vào thiết kế thông minh và tự động. Việc áp dụng các hệ thống điều khiển và thuật toán tiên tiến sẽ cho phép thiết bị tự động điều chỉnh các thông số cắt để phù hợp với các yêu cầu thiết kế và vật liệu khác nhau, từ đó cải thiện đáng kể hiệu quả sản xuất. Những cải tiến như công nghệ cắt nhiều wafer và hệ thống thay lưỡi dao nhanh chóng sẽ đóng vai trò quan trọng trong việc nâng cao hiệu quả.

Giảm chi phí:

Giảm chi phí là hướng đi then chốt cho sự phát triển của công nghệ cắt wafer. Khi vật liệu và phương pháp cắt mới được phát triển, chi phí thiết bị và chi phí bảo trì dự kiến sẽ được kiểm soát hiệu quả. Ngoài ra, việc tối ưu hóa quy trình sản xuất và giảm tỷ lệ phế liệu sẽ tiếp tục giảm thiểu chất thải trong quá trình sản xuất, dẫn đến giảm tổng chi phí sản xuất.

Sản xuất thông minh và IoT:

Việc tích hợp công nghệ sản xuất thông minh và Internet vạn vật (IoT) sẽ mang lại những thay đổi mang tính đột phá cho công nghệ cắt wafer. Thông qua khả năng kết nối và chia sẻ dữ liệu giữa các thiết bị, mọi bước của quy trình sản xuất đều có thể được giám sát và tối ưu hóa theo thời gian thực. Điều này không chỉ cải thiện hiệu quả sản xuất và chất lượng sản phẩm mà còn cung cấp cho các công ty khả năng dự báo thị trường và hỗ trợ ra quyết định chính xác hơn.

Trong tương lai, công nghệ cắt wafer sẽ đạt được những tiến bộ vượt bậc về độ chính xác, hiệu quả và chi phí. Những tiến bộ này sẽ thúc đẩy sự phát triển liên tục của ngành công nghiệp bán dẫn và mang lại nhiều cải tiến công nghệ và tiện ích hơn cho xã hội loài người.

Thời gian đăng: 19-11-2024