Năm 1965, người đồng sáng lập Intel, Gordon Moore, đã đưa ra định luật mà sau này được gọi là “Định luật Moore”. Trong hơn nửa thế kỷ, định luật này đã tạo nền tảng cho sự gia tăng ổn định về hiệu năng của mạch tích hợp (IC) và giảm chi phí – nền tảng của công nghệ kỹ thuật số hiện đại. Nói tóm lại: số lượng bóng bán dẫn trên một con chip tăng gấp đôi sau mỗi hai năm.

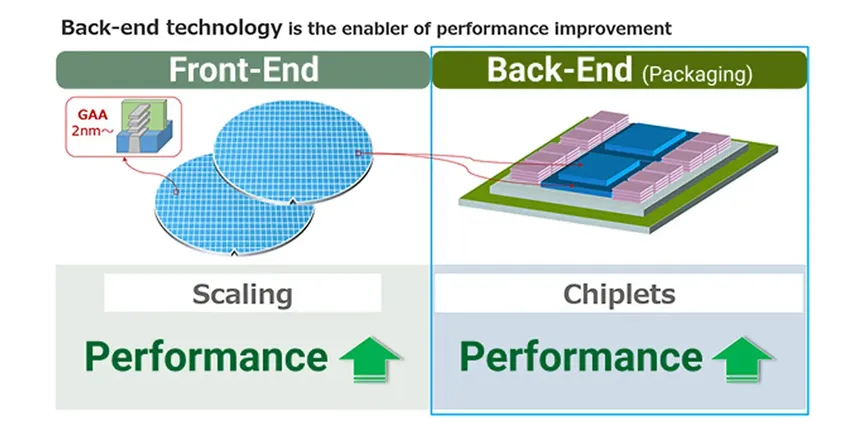

Trong nhiều năm, tiến bộ luôn theo nhịp độ đó. Giờ đây, bức tranh đang thay đổi. Việc thu nhỏ hơn nữa ngày càng khó khăn; kích thước các chi tiết chỉ còn vài nanomet. Các kỹ sư đang gặp phải những giới hạn vật lý, các bước quy trình phức tạp hơn và chi phí tăng cao. Kích thước nhỏ hơn cũng làm giảm năng suất, khiến việc sản xuất hàng loạt trở nên khó khăn hơn. Xây dựng và vận hành một nhà máy sản xuất tiên tiến đòi hỏi nguồn vốn và chuyên môn khổng lồ. Do đó, nhiều người cho rằng Định luật Moore đang mất dần động lực.

Sự thay đổi đó đã mở ra một hướng tiếp cận mới: chiplet.

Chiplet là một chip nhỏ thực hiện một chức năng cụ thể—về cơ bản là một phần của chip nguyên khối duy nhất trước đây. Bằng cách tích hợp nhiều chiplet trong một gói duy nhất, các nhà sản xuất có thể lắp ráp một hệ thống hoàn chỉnh.

Trong kỷ nguyên chip nguyên khối, tất cả các chức năng đều nằm trên một chip lớn duy nhất, vì vậy một lỗi nhỏ ở bất kỳ đâu cũng có thể làm hỏng toàn bộ chip. Với chiplet, các hệ thống được xây dựng từ "chip đã được kiểm chứng chất lượng" (KGD), giúp cải thiện đáng kể năng suất và hiệu quả sản xuất.

Việc tích hợp không đồng nhất—kết hợp các chip được xây dựng trên các công nghệ khác nhau và cho các chức năng khác nhau—làm cho các chiplet trở nên đặc biệt mạnh mẽ. Các khối tính toán hiệu năng cao có thể sử dụng các công nghệ mới nhất, trong khi bộ nhớ và mạch tương tự vẫn sử dụng các công nghệ đã hoàn thiện và tiết kiệm chi phí. Kết quả: hiệu năng cao hơn với chi phí thấp hơn.

Ngành công nghiệp ô tô đặc biệt quan tâm. Các nhà sản xuất ô tô lớn đang sử dụng các kỹ thuật này để phát triển các SoC trong xe hơi thế hệ tương lai, với mục tiêu áp dụng rộng rãi sau năm 2030. Chiplet cho phép họ mở rộng quy mô AI và đồ họa hiệu quả hơn đồng thời cải thiện năng suất – từ đó nâng cao cả hiệu năng và chức năng trong chất bán dẫn ô tô.

Một số bộ phận ô tô phải đáp ứng các tiêu chuẩn an toàn chức năng nghiêm ngặt và do đó phải dựa vào các công nghệ sản xuất cũ, đã được chứng minh. Trong khi đó, các hệ thống hiện đại như hệ thống hỗ trợ lái xe tiên tiến (ADAS) và xe điều khiển bằng phần mềm (SDV) đòi hỏi khả năng tính toán cao hơn nhiều. Chiplet giúp thu hẹp khoảng cách đó: bằng cách kết hợp các bộ vi điều khiển an toàn, bộ nhớ lớn và bộ tăng tốc AI mạnh mẽ, các nhà sản xuất có thể tùy chỉnh SoC cho phù hợp với nhu cầu của từng nhà sản xuất ô tô — nhanh hơn.

Những ưu điểm này không chỉ giới hạn trong lĩnh vực ô tô. Kiến trúc chiplet đang lan rộng sang lĩnh vực trí tuệ nhân tạo, viễn thông và các lĩnh vực khác, thúc đẩy đổi mới trong toàn ngành và nhanh chóng trở thành trụ cột trong lộ trình phát triển chất bán dẫn.

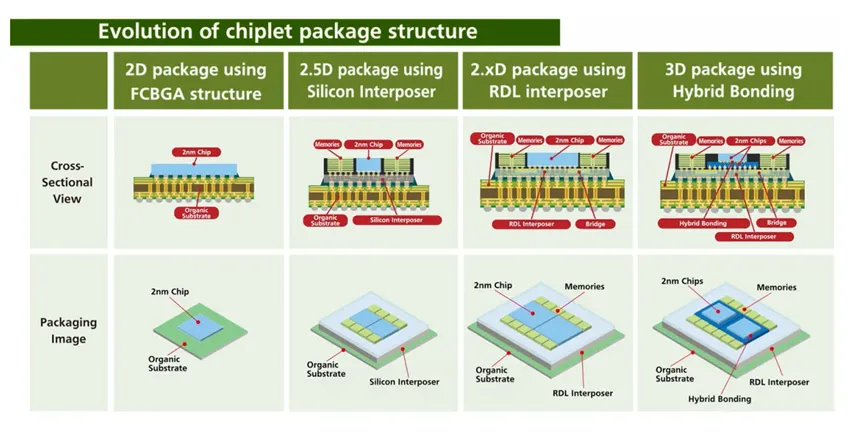

Việc tích hợp chiplet phụ thuộc vào các kết nối giữa các chip nhỏ gọn và tốc độ cao. Yếu tố then chốt là lớp trung gian (interposer) – một lớp trung gian, thường là silicon, nằm bên dưới các chip, có chức năng dẫn truyền tín hiệu giống như một bảng mạch nhỏ. Lớp trung gian tốt hơn đồng nghĩa với sự kết nối chặt chẽ hơn và tốc độ trao đổi tín hiệu nhanh hơn.

Công nghệ đóng gói tiên tiến cũng giúp cải thiện khả năng truyền tải điện năng. Các mảng dày đặc các kết nối kim loại nhỏ giữa các chip cung cấp đủ đường dẫn cho dòng điện và dữ liệu ngay cả trong không gian chật hẹp, cho phép truyền tải băng thông cao đồng thời sử dụng hiệu quả diện tích đóng gói hạn chế.

Phương pháp phổ biến hiện nay là tích hợp 2.5D: đặt nhiều chip cạnh nhau trên một lớp trung gian. Bước tiến tiếp theo là tích hợp 3D, xếp chồng các chip theo chiều dọc bằng cách sử dụng các đường dẫn xuyên silicon (TSV) để đạt mật độ cao hơn nữa.

Việc kết hợp thiết kế chip dạng mô-đun (tách biệt chức năng và loại mạch) với công nghệ xếp chồng 3D tạo ra các chất bán dẫn nhanh hơn, nhỏ hơn và tiết kiệm năng lượng hơn. Việc đặt bộ nhớ và khả năng tính toán cùng vị trí mang lại băng thông khổng lồ cho các tập dữ liệu lớn — lý tưởng cho trí tuệ nhân tạo và các tác vụ hiệu năng cao khác.

Tuy nhiên, việc xếp chồng theo chiều dọc lại mang đến những thách thức. Nhiệt tích tụ dễ dàng hơn, làm phức tạp việc quản lý nhiệt và năng suất. Để giải quyết vấn đề này, các nhà nghiên cứu đang phát triển các phương pháp đóng gói mới để xử lý tốt hơn các hạn chế về nhiệt. Mặc dù vậy, động lực vẫn rất mạnh mẽ: sự hội tụ của các chiplet và tích hợp 3D được xem là một mô hình đột phá—sẵn sàng tiếp nối thành công của Định luật Moore.

Thời gian đăng bài: 15 tháng 10 năm 2025