Trong quá trình phát triển bùng nổ của ngành công nghiệp bán dẫn, tinh thể đơn được đánh bóng.tấm siliconChúng đóng vai trò vô cùng quan trọng. Chúng là vật liệu cơ bản cho việc sản xuất nhiều thiết bị vi điện tử khác nhau. Từ các mạch tích hợp phức tạp và chính xác đến bộ vi xử lý tốc độ cao và cảm biến đa chức năng, tinh thể đơn được đánh bóng đều đóng vai trò thiết yếu.tấm siliconChúng rất cần thiết. Sự khác biệt về hiệu suất và thông số kỹ thuật của chúng ảnh hưởng trực tiếp đến chất lượng và hiệu suất của sản phẩm cuối cùng. Dưới đây là các thông số kỹ thuật và thông số phổ biến của các tấm wafer silicon đơn tinh thể được đánh bóng:

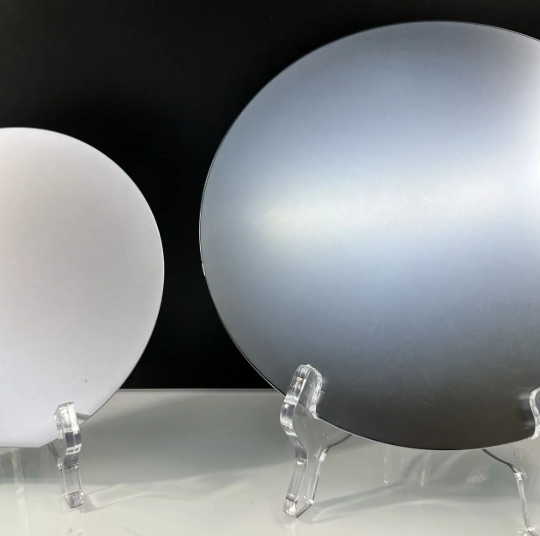

Đường kính: Kích thước của các tấm bán dẫn silicon đơn tinh thể được đo bằng đường kính của chúng, và chúng có nhiều thông số kỹ thuật khác nhau. Các đường kính phổ biến bao gồm 2 inch (50,8mm), 3 inch (76,2mm), 4 inch (100mm), 5 inch (125mm), 6 inch (150mm), 8 inch (200mm), 12 inch (300mm) và 18 inch (450mm). Các đường kính khác nhau phù hợp với các nhu cầu sản xuất và yêu cầu quy trình khác nhau. Ví dụ, các tấm có đường kính nhỏ hơn thường được sử dụng cho các thiết bị vi điện tử đặc biệt, có khối lượng nhỏ, trong khi các tấm có đường kính lớn hơn thể hiện hiệu quả sản xuất cao hơn và lợi thế về chi phí trong sản xuất mạch tích hợp quy mô lớn. Yêu cầu về bề mặt được phân loại là đánh bóng một mặt (SSP) và đánh bóng hai mặt (DSP). Các tấm đánh bóng một mặt được sử dụng cho các thiết bị yêu cầu độ phẳng cao ở một mặt, chẳng hạn như một số loại cảm biến. Các tấm đánh bóng hai mặt thường được sử dụng cho các mạch tích hợp và các sản phẩm khác yêu cầu độ chính xác cao trên cả hai bề mặt. Yêu cầu về bề mặt (Độ hoàn thiện): SSP đánh bóng một mặt / DSP đánh bóng hai mặt.

Loại/Chất pha tạp: (1) Bán dẫn loại N: Khi một số nguyên tử tạp chất được đưa vào bán dẫn nội tại, chúng làm thay đổi độ dẫn điện của nó. Ví dụ, khi các nguyên tố hóa trị năm như nitơ (N), phốt pho (P), asen (As) hoặc antimon (Sb) được thêm vào, các electron hóa trị của chúng tạo thành liên kết cộng hóa trị với các electron hóa trị của các nguyên tử silic xung quanh, để lại một electron dư thừa không bị ràng buộc bởi liên kết cộng hóa trị. Điều này dẫn đến nồng độ electron lớn hơn nồng độ lỗ trống, tạo thành bán dẫn loại N, còn được gọi là bán dẫn loại electron. Bán dẫn loại N rất quan trọng trong sản xuất các thiết bị yêu cầu electron làm chất mang điện chính, chẳng hạn như một số thiết bị điện. (2) Bán dẫn loại P: Khi các nguyên tố tạp chất hóa trị ba như boron (B), gali (Ga) hoặc indi (In) được đưa vào bán dẫn silic, các electron hóa trị của các nguyên tử tạp chất tạo thành liên kết cộng hóa trị với các nguyên tử silic xung quanh, nhưng chúng thiếu ít nhất một electron hóa trị và không thể tạo thành liên kết cộng hóa trị hoàn chỉnh. Điều này dẫn đến nồng độ lỗ trống lớn hơn nồng độ electron, tạo thành chất bán dẫn loại P, còn được gọi là chất bán dẫn loại lỗ trống. Chất bán dẫn loại P đóng vai trò quan trọng trong sản xuất các thiết bị mà lỗ trống đóng vai trò là chất mang điện chính, chẳng hạn như điốt và một số loại bóng bán dẫn.

Điện trở suất: Điện trở suất là một đại lượng vật lý quan trọng đo lường độ dẫn điện của các tấm silicon đơn tinh thể đã được đánh bóng. Giá trị của nó phản ánh hiệu suất dẫn điện của vật liệu. Điện trở suất càng thấp, độ dẫn điện của tấm silicon càng tốt; ngược lại, điện trở suất càng cao, độ dẫn điện càng kém. Điện trở suất của các tấm silicon được xác định bởi các đặc tính vật liệu vốn có của chúng, và nhiệt độ cũng có tác động đáng kể. Nói chung, điện trở suất của các tấm silicon tăng theo nhiệt độ. Trong các ứng dụng thực tế, các thiết bị vi điện tử khác nhau có yêu cầu về điện trở suất khác nhau đối với các tấm silicon. Ví dụ, các tấm silicon được sử dụng trong sản xuất mạch tích hợp cần kiểm soát chính xác điện trở suất để đảm bảo hiệu suất thiết bị ổn định và đáng tin cậy.

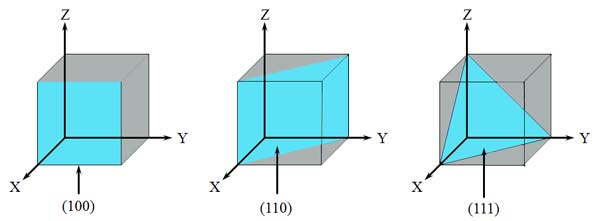

Hướng tinh thể: Hướng tinh thể của tấm wafer thể hiện hướng tinh thể học của mạng lưới silicon, thường được xác định bằng các chỉ số Miller như (100), (110), (111), v.v. Các hướng tinh thể khác nhau có các tính chất vật lý khác nhau, chẳng hạn như mật độ đường kẻ, thay đổi tùy thuộc vào hướng. Sự khác biệt này có thể ảnh hưởng đến hiệu suất của tấm wafer trong các bước xử lý tiếp theo và hiệu suất cuối cùng của các thiết bị vi điện tử. Trong quá trình sản xuất, việc lựa chọn tấm wafer silicon có hướng phù hợp với các yêu cầu thiết bị khác nhau có thể tối ưu hóa hiệu suất thiết bị, cải thiện hiệu quả sản xuất và nâng cao chất lượng sản phẩm.

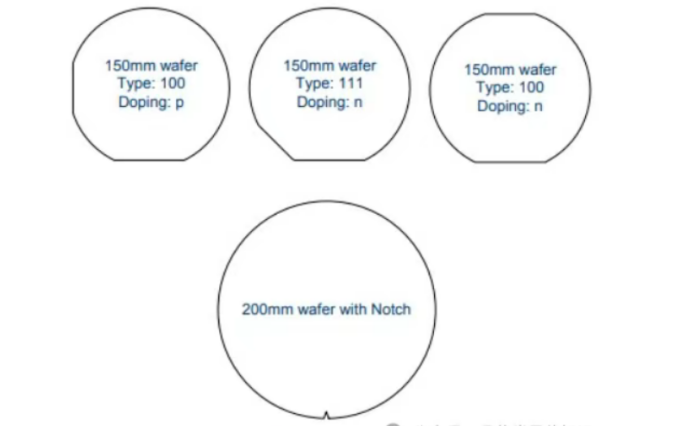

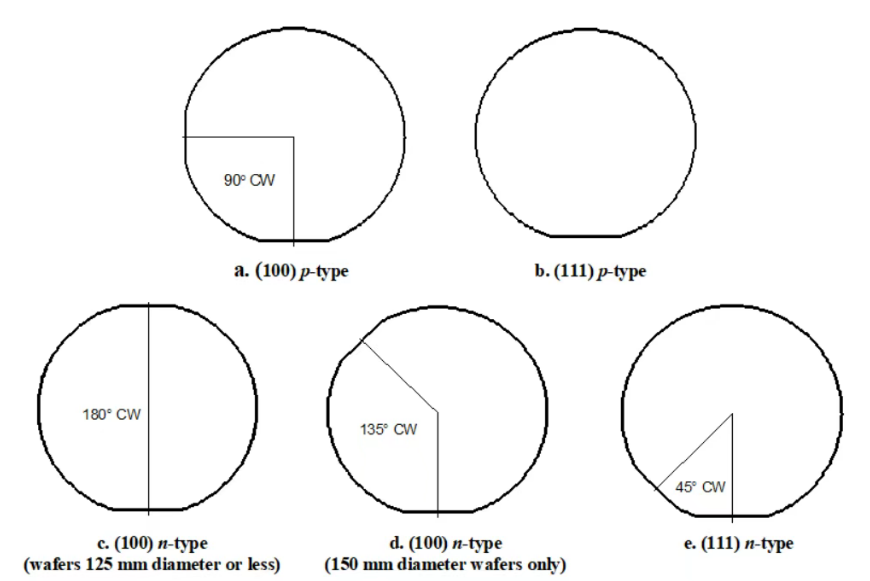

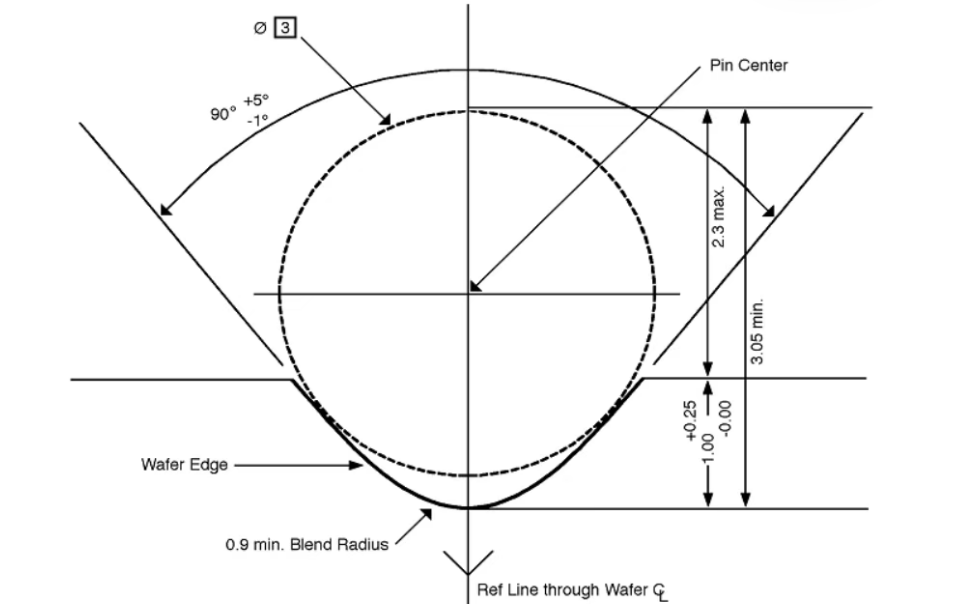

Mặt phẳng/Vết khía: Mặt phẳng (Flat) hoặc vết khía hình chữ V (Notch) trên chu vi của tấm silicon đóng vai trò quan trọng trong việc định hướng tinh thể và là một dấu hiệu nhận biết quan trọng trong quá trình sản xuất và gia công tấm wafer. Các tấm wafer có đường kính khác nhau tương ứng với các tiêu chuẩn khác nhau về chiều dài của mặt phẳng hoặc vết khía. Các cạnh định hướng được phân loại thành mặt phẳng chính và mặt phẳng phụ. Mặt phẳng chính chủ yếu được sử dụng để xác định hướng tinh thể cơ bản và tham chiếu gia công của tấm wafer, trong khi mặt phẳng phụ hỗ trợ thêm cho việc định hướng và gia công chính xác, đảm bảo hoạt động chính xác và tính nhất quán của tấm wafer trong suốt dây chuyền sản xuất.

Độ dày: Độ dày của tấm bán dẫn thường được chỉ định bằng micromet (μm), với phạm vi độ dày phổ biến từ 100μm đến 1000μm. Các tấm bán dẫn có độ dày khác nhau phù hợp với các loại thiết bị vi điện tử khác nhau. Các tấm bán dẫn mỏng hơn (ví dụ: 100μm – 300μm) thường được sử dụng trong sản xuất chip đòi hỏi kiểm soát độ dày nghiêm ngặt, giúp giảm kích thước và trọng lượng của chip, đồng thời tăng mật độ tích hợp. Các tấm bán dẫn dày hơn (ví dụ: 500μm – 1000μm) được sử dụng rộng rãi trong các thiết bị yêu cầu độ bền cơ học cao hơn, chẳng hạn như các thiết bị bán dẫn công suất, để đảm bảo sự ổn định trong quá trình hoạt động.

Độ nhám bề mặt: Độ nhám bề mặt là một trong những thông số quan trọng để đánh giá chất lượng wafer, vì nó ảnh hưởng trực tiếp đến độ bám dính giữa wafer và các vật liệu màng mỏng được lắng đọng sau đó, cũng như hiệu suất điện của thiết bị. Nó thường được biểu thị bằng độ nhám trung bình bình phương (RMS) (tính bằng nm). Độ nhám bề mặt càng thấp thì bề mặt wafer càng mịn, giúp giảm các hiện tượng như tán xạ electron và cải thiện hiệu suất cũng như độ tin cậy của thiết bị. Trong các quy trình sản xuất chất bán dẫn tiên tiến, yêu cầu về độ nhám bề mặt ngày càng trở nên nghiêm ngặt, đặc biệt là đối với sản xuất mạch tích hợp cao cấp, nơi độ nhám bề mặt phải được kiểm soát ở mức vài nanomet hoặc thậm chí thấp hơn.

Biến thiên độ dày tổng thể (TTV): Biến thiên độ dày tổng thể đề cập đến sự khác biệt giữa độ dày tối đa và tối thiểu được đo tại nhiều điểm trên bề mặt tấm wafer, thường được biểu thị bằng μm. TTV cao có thể dẫn đến sai lệch trong các quy trình như quang khắc và khắc axit, ảnh hưởng đến tính nhất quán về hiệu suất và năng suất của thiết bị. Do đó, kiểm soát TTV trong quá trình sản xuất wafer là một bước quan trọng để đảm bảo chất lượng sản phẩm. Đối với sản xuất thiết bị vi điện tử có độ chính xác cao, TTV thường được yêu cầu nằm trong phạm vi vài micromet.

Độ cong: Độ cong đề cập đến độ lệch giữa bề mặt tấm bán dẫn và mặt phẳng lý tưởng, thường được đo bằng micromet. Các tấm bán dẫn bị cong quá mức có thể bị vỡ hoặc chịu ứng suất không đều trong quá trình gia công tiếp theo, ảnh hưởng đến hiệu quả sản xuất và chất lượng sản phẩm. Đặc biệt trong các quy trình yêu cầu độ phẳng cao, chẳng hạn như quang khắc, độ cong phải được kiểm soát trong một phạm vi cụ thể để đảm bảo độ chính xác và tính nhất quán của mẫu quang khắc.

Độ cong vênh: Độ cong vênh biểu thị sự sai lệch giữa bề mặt wafer và hình dạng cầu lý tưởng, cũng được đo bằng micromet. Tương tự như độ cong, độ cong vênh là một chỉ số quan trọng về độ phẳng của wafer. Độ cong vênh quá mức không chỉ ảnh hưởng đến độ chính xác khi đặt wafer vào thiết bị xử lý mà còn có thể gây ra các vấn đề trong quá trình đóng gói chip, chẳng hạn như liên kết kém giữa chip và vật liệu đóng gói, từ đó ảnh hưởng đến độ tin cậy của thiết bị. Trong sản xuất chất bán dẫn cao cấp, yêu cầu về độ cong vênh ngày càng khắt khe hơn để đáp ứng nhu cầu của các quy trình sản xuất và đóng gói chip tiên tiến.

Hình dạng cạnh: Hình dạng cạnh của tấm bán dẫn rất quan trọng đối với quá trình xử lý và thao tác tiếp theo. Nó thường được xác định bởi Vùng Loại trừ Cạnh (EEZ), xác định khoảng cách từ cạnh tấm bán dẫn mà không được phép xử lý. Một hình dạng cạnh được thiết kế đúng cách và kiểm soát EEZ chính xác giúp tránh các khuyết tật ở cạnh, sự tập trung ứng suất và các vấn đề khác trong quá trình xử lý, cải thiện chất lượng và năng suất tổng thể của tấm bán dẫn. Trong một số quy trình sản xuất tiên tiến, độ chính xác của hình dạng cạnh cần phải đạt mức dưới micromet.

Số lượng hạt: Số lượng và sự phân bố kích thước của các hạt trên bề mặt tấm bán dẫn ảnh hưởng đáng kể đến hiệu suất của các thiết bị vi điện tử. Các hạt quá nhiều hoặc có kích thước lớn có thể dẫn đến hỏng hóc thiết bị, chẳng hạn như đoản mạch hoặc rò rỉ, làm giảm năng suất sản phẩm. Do đó, số lượng hạt thường được đo bằng cách đếm số hạt trên một đơn vị diện tích, ví dụ như số hạt lớn hơn 0,3μm. Kiểm soát chặt chẽ số lượng hạt trong quá trình sản xuất tấm bán dẫn là một biện pháp thiết yếu để đảm bảo chất lượng sản phẩm. Các công nghệ làm sạch tiên tiến và môi trường sản xuất sạch sẽ được sử dụng để giảm thiểu sự nhiễm bẩn hạt trên bề mặt tấm bán dẫn.

![]()

![]()

![]()

![]()

![]()

Sản xuất liên quan

Tấm wafer silicon đơn tinh thể, chất nền Si, loại N/P, tùy chọn tấm wafer silicon carbide.

Tấm wafer silicon FZ CZ có sẵn, kích thước 12 inch, hàng chính hãng hoặc hàng đã qua kiểm tra.

Thời gian đăng bài: 18/04/2025