Tấm wafer LNOI (Lithium Niobate trên chất cách điện) Viễn thông Cảm biến Điện quang cao cấp

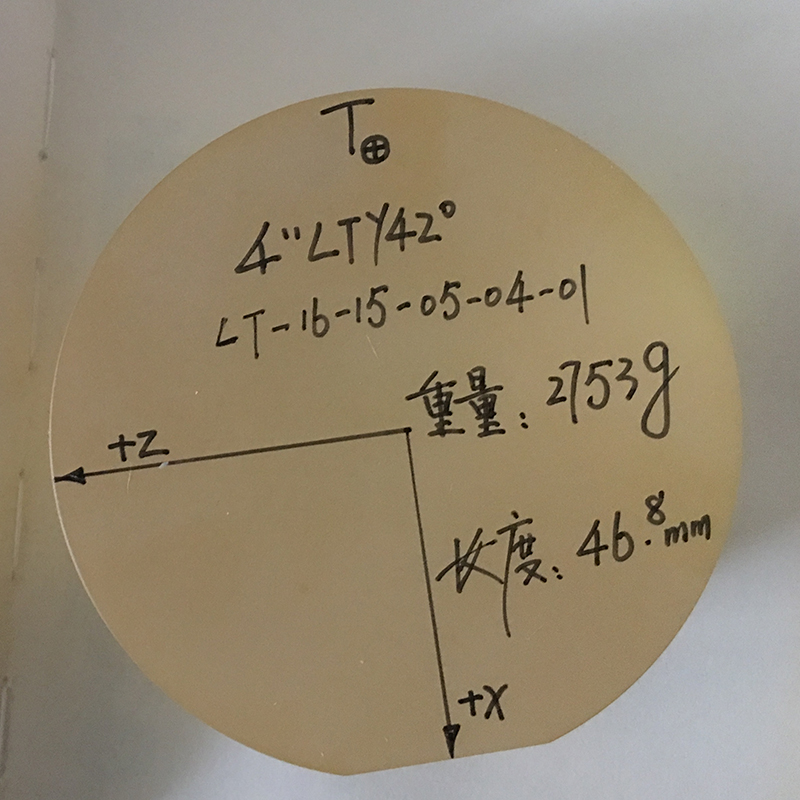

Sơ đồ chi tiết

Tổng quan

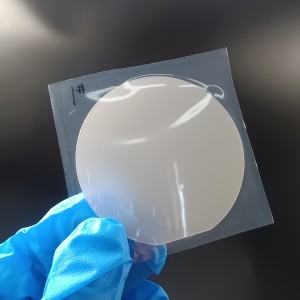

Bên trong hộp đựng wafer có các rãnh đối xứng, kích thước hoàn toàn đồng nhất để đỡ hai mặt của wafer. Hộp đựng wafer thường được làm bằng vật liệu nhựa PP trong suốt, có khả năng chịu nhiệt, chống mài mòn và chống tĩnh điện. Các chất phụ gia có màu sắc khác nhau được sử dụng để phân biệt các phân đoạn xử lý kim loại trong sản xuất chất bán dẫn. Do kích thước nhỏ của các linh kiện bán dẫn, cấu trúc dày đặc và yêu cầu kích thước hạt rất nghiêm ngặt trong sản xuất, hộp đựng wafer phải đảm bảo môi trường sạch sẽ để kết nối với khoang phản ứng vi môi trường của các máy sản xuất khác nhau.

Phương pháp chế tạo

Quá trình chế tạo các tấm bán dẫn LNOI bao gồm một số bước chính xác:

Bước 1: Cấy ghép ion heliCác ion heli được đưa vào tinh thể LN khối bằng máy cấy ion. Các ion này sẽ lắng đọng ở một độ sâu cụ thể, tạo thành một mặt phẳng yếu hơn, cuối cùng sẽ tạo điều kiện thuận lợi cho việc tách màng.

Bước 2: Tạo lớp nềnMột tấm wafer silicon hoặc LN riêng biệt được oxy hóa hoặc phủ một lớp SiO2 bằng phương pháp PECVD hoặc oxy hóa nhiệt. Bề mặt trên cùng của nó được làm phẳng để tối ưu hóa quá trình liên kết.

Bước 3: Liên kết LN với chất nềnTinh thể LN được cấy ion được lật ngược và gắn vào đế wafer bằng phương pháp liên kết wafer trực tiếp. Trong môi trường nghiên cứu, benzocyclobutene (BCB) có thể được sử dụng làm chất kết dính để đơn giản hóa quá trình liên kết trong điều kiện ít khắt khe hơn.

Bước 4: Xử lý nhiệt và tách màngQuá trình ủ nhiệt kích hoạt sự hình thành bọt khí ở độ sâu được cấy ghép, cho phép tách lớp màng mỏng (lớp LN trên cùng) khỏi phần vật liệu chính. Lực cơ học được sử dụng để hoàn tất quá trình bóc tách.

Bước 5: Đánh bóng bề mặtPhương pháp đánh bóng cơ học hóa học (CMP) được áp dụng để làm mịn bề mặt LN phía trên, cải thiện chất lượng quang học và năng suất thiết bị.

Thông số kỹ thuật

| Vật liệu | Quang học Cấp LiNbO3 bánh quế (màu trắng) or Đen) | |

| Curie Nhiệt độ | 1142±0,7℃ | |

| Cắt Góc | X/Y/Z, v.v. | |

| Đường kính/kích thước | 2”/3”/4” ±0.03mm | |

| Tol(±) | <0,20 mm ±0,005 mm | |

| Độ dày | 0,18~0,5mm trở lên | |

| Sơ đẳng Phẳng | 16mm/22mm/32mm | |

| TTV | <3μm | |

| Cây cung | -30 | |

| Biến dạng | <40μm | |

| Định hướng Phẳng | Tất cả đều có sẵn | |

| Bề mặt Kiểu | Đánh bóng một mặt (SSP)/Đánh bóng hai mặt (DSP) | |

| Đánh bóng bên Ra | <0,5nm | |

| S/D | 20/10 | |

| Bờ rìa Tiêu chuẩn | R=0,2mm Loại C or Mũi bò | |

| Chất lượng | Miễn phí of nứt (bong bóng) Và bao gồm) | |

| Quang học pha tạp | Mg/Fe/Zn/MgO vân vân vì quang học cấp LN bánh wafer mỗi yêu cầu | |

| Bánh wafer Bề mặt Tiêu chuẩn | Chỉ số khúc xạ | No=2.2878/Ne=2.2033 @ bước sóng 632nm/phương pháp ghép lăng kính. |

| Sự ô nhiễm, | Không có | |

| Các hạt c>0,3μ m | <=30 | |

| Trầy xước, sứt mẻ | Không có | |

| Khuyết điểm | Không có vết nứt cạnh, vết xước, vết cưa, vết bẩn. | |

| Bao bì | Số lượng/Hộp bánh wafer | 25 chiếc mỗi hộp |

Các trường hợp sử dụng

Nhờ tính linh hoạt và hiệu suất cao, LNOI được sử dụng rộng rãi trong nhiều ngành công nghiệp:

Quang học:Các bộ điều biến, bộ ghép kênh và mạch quang học nhỏ gọn.

Tần số vô tuyến/Âm học:Bộ điều biến quang âm, bộ lọc tần số vô tuyến.

Máy tính lượng tử:Bộ trộn tần số phi tuyến và bộ tạo cặp photon.

Quốc phòng & Hàng không vũ trụ:Con quay hồi chuyển quang học tổn hao thấp, thiết bị dịch tần số.

Thiết bị y tế:Cảm biến sinh học quang học và đầu dò tín hiệu tần số cao.

Câu hỏi thường gặp

Hỏi: Tại sao LNOI được ưa chuộng hơn SOI trong các hệ thống quang học?

A:LNOI sở hữu hệ số điện quang vượt trội và phạm vi trong suốt rộng hơn, cho phép hiệu suất cao hơn trong các mạch quang tử.

Hỏi: Việc quản lý hợp đồng (CMP) có bắt buộc sau khi chia tách doanh nghiệp không?

A:Đúng vậy. Bề mặt LN lộ ra sau khi cắt bằng ion khá thô ráp và cần phải được đánh bóng để đáp ứng các thông số kỹ thuật quang học.

Hỏi: Kích thước wafer tối đa hiện có là bao nhiêu?

A:Các tấm wafer LNOI thương mại chủ yếu có kích thước 3” và 4”, mặc dù một số nhà cung cấp đang phát triển các phiên bản 6”.

Hỏi: Lớp LN có thể được tái sử dụng sau khi tách không?

A:Tinh thể nền có thể được đánh bóng lại và tái sử dụng nhiều lần, mặc dù chất lượng có thể giảm sút sau nhiều chu kỳ.

Hỏi: Các tấm wafer LNOI có tương thích với quy trình CMOS không?

A:Đúng vậy, chúng được thiết kế để phù hợp với các quy trình chế tạo chất bán dẫn thông thường, đặc biệt là khi sử dụng chất nền silicon.