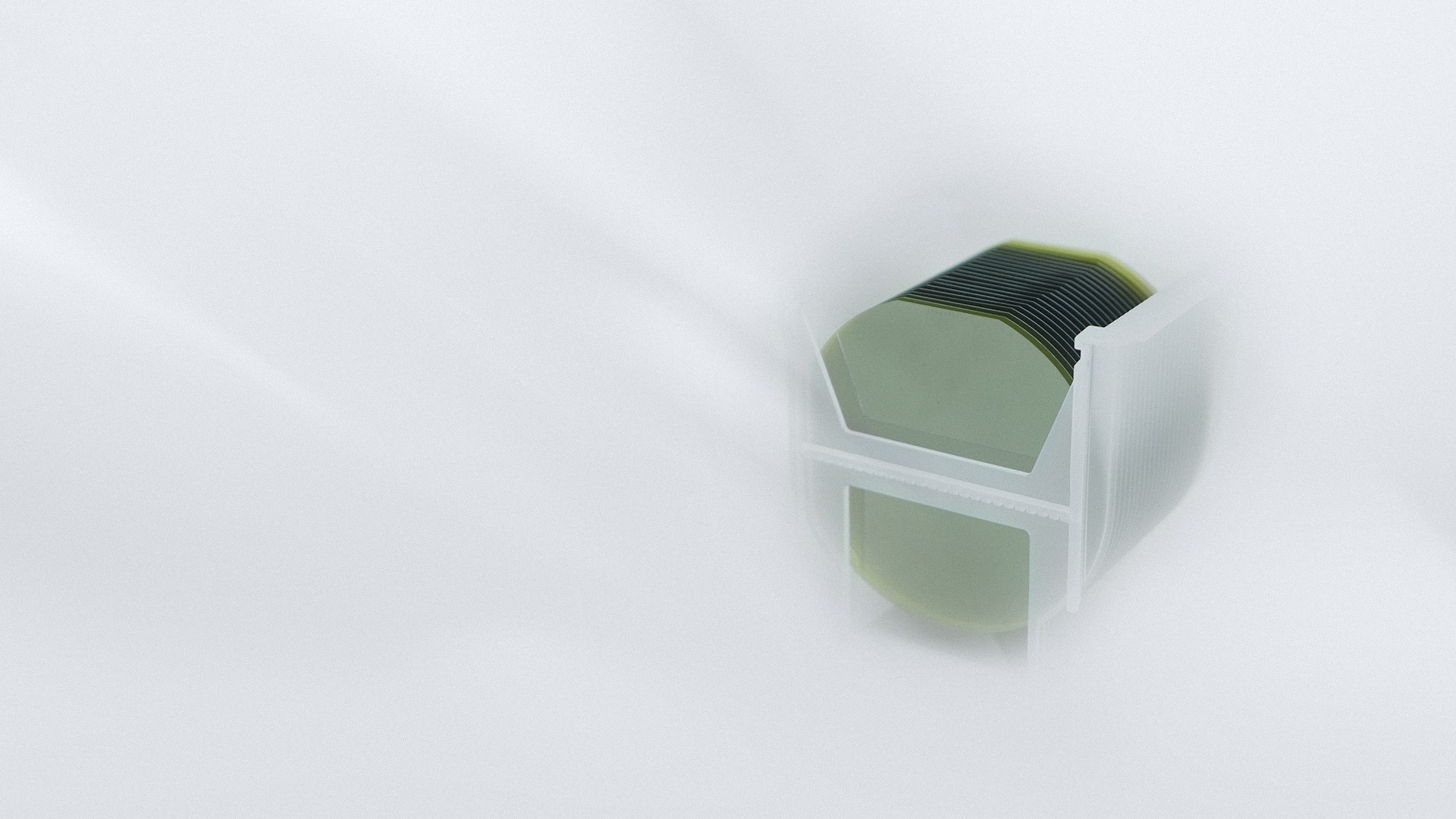

Tấm wafer SiC 4H-N HPSI, tấm wafer SiC 6H-N, 6H-P, 3C-N dạng màng mỏng dùng cho MOS hoặc SBD.

Tóm tắt về chất nền SiC, tấm bán dẫn SiC Epi-wafer

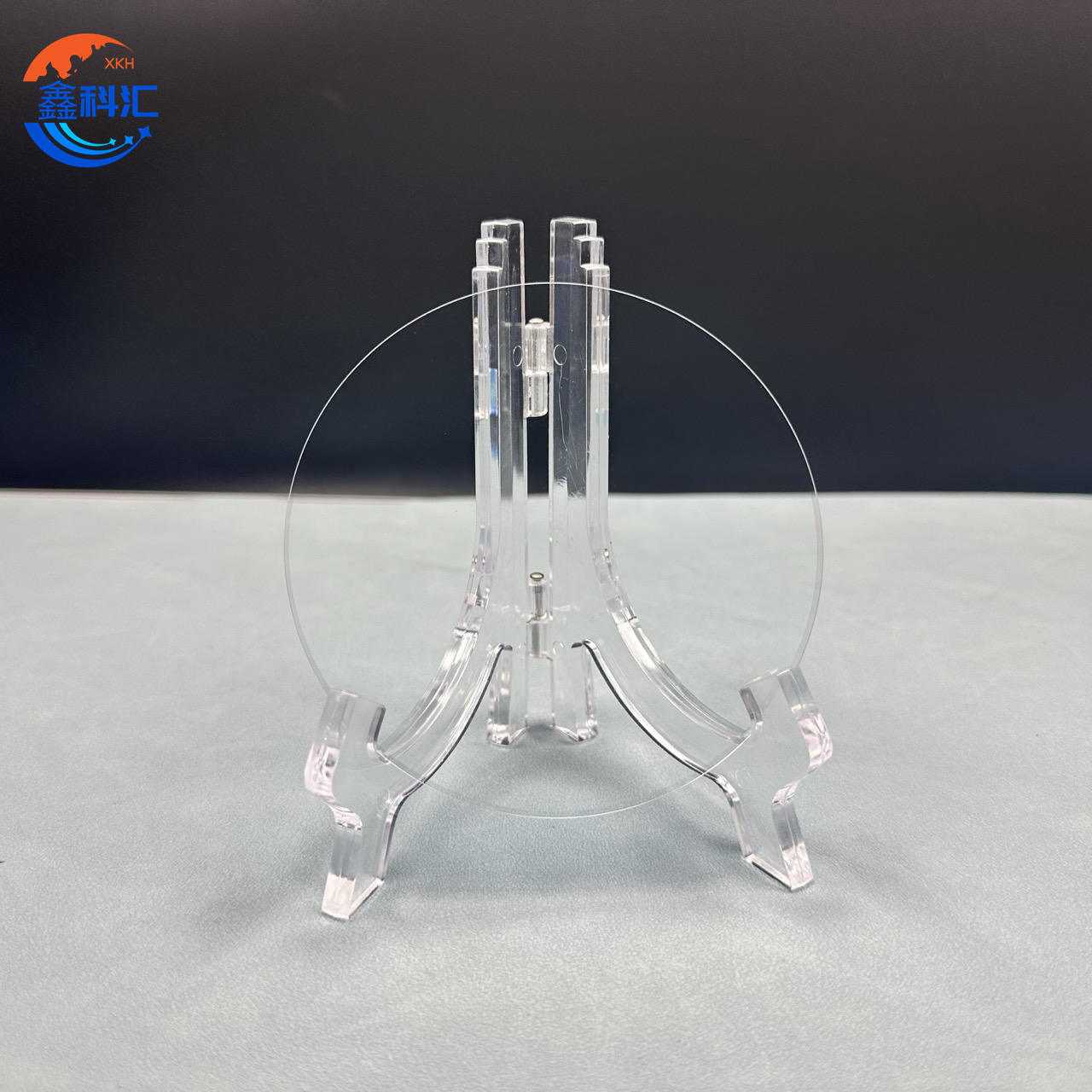

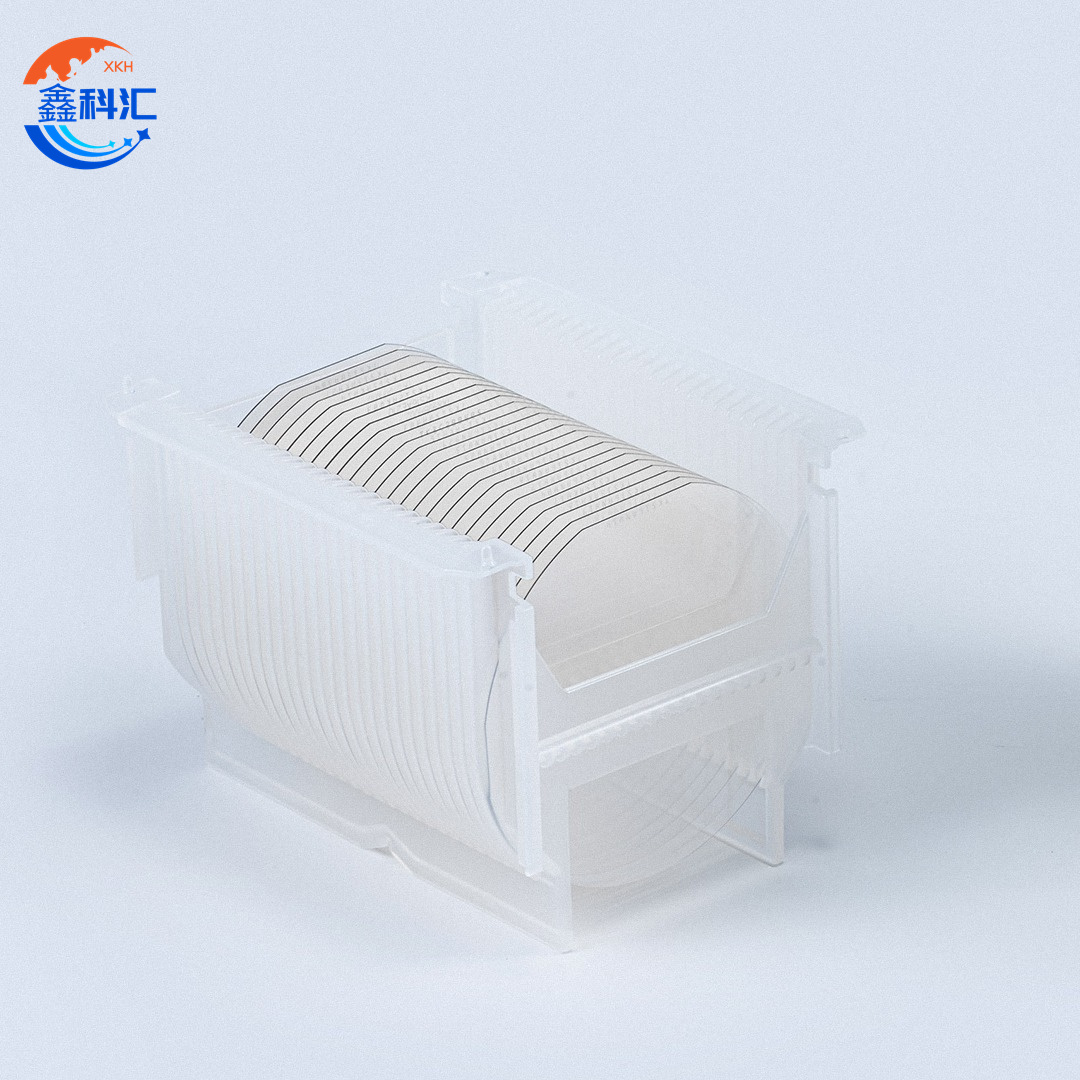

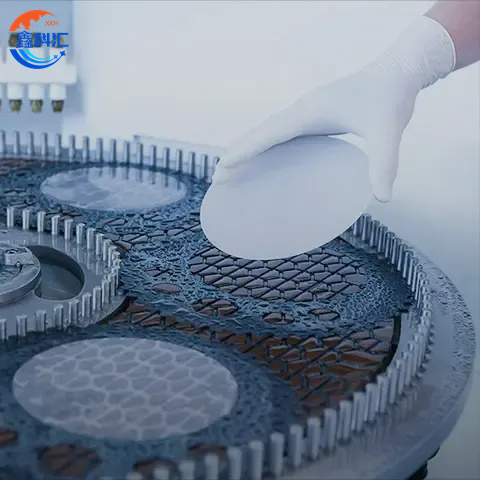

Chúng tôi cung cấp đầy đủ các loại chất nền SiC và tấm wafer SiC chất lượng cao với nhiều dạng đa hình và cấu hình pha tạp khác nhau—bao gồm 4H-N (dẫn điện loại n), 4H-P (dẫn điện loại p), 4H-HPSI (bán cách điện độ tinh khiết cao) và 6H-P (dẫn điện loại p)—với đường kính từ 4″, 6″ và 8″ đến 12″. Bên cạnh chất nền trần, dịch vụ tăng trưởng wafer epitaxy (epi) giá trị gia tăng của chúng tôi cung cấp các wafer epitaxy với độ dày (1–20 µm), nồng độ pha tạp và mật độ khuyết tật được kiểm soát chặt chẽ.

Mỗi tấm wafer SiC và wafer epitaxy đều trải qua quá trình kiểm tra nghiêm ngặt trên dây chuyền sản xuất (mật độ vi ống <0,1 cm⁻², độ nhám bề mặt Ra <0,2 nm) và đặc tính điện đầy đủ (CV, lập bản đồ điện trở suất) để đảm bảo độ đồng nhất tinh thể và hiệu suất vượt trội. Cho dù được sử dụng cho các mô-đun điện tử công suất, bộ khuếch đại RF tần số cao hay các thiết bị quang điện tử (LED, bộ tách sóng quang), dòng sản phẩm wafer SiC và wafer epitaxy của chúng tôi đều mang lại độ tin cậy, độ ổn định nhiệt và độ bền điện môi cần thiết cho các ứng dụng đòi hỏi khắt khe nhất hiện nay.

Tính chất và ứng dụng của chất nền SiC loại 4H-N

-

Cấu trúc đa hình (lục giác) của chất nền SiC 4H-N

Khoảng cách vùng cấm rộng ~3,26 eV đảm bảo hiệu suất điện ổn định và khả năng chịu nhiệt tốt trong điều kiện nhiệt độ cao và điện trường cao.

-

Chất nền SiCPha tạp loại N

Việc pha tạp nitơ được kiểm soát chính xác tạo ra nồng độ hạt tải điện từ 1×10¹⁶ đến 1×10¹⁹ cm⁻³ và độ linh động điện tử ở nhiệt độ phòng lên đến ~900 cm²/V·s, giảm thiểu tổn thất dẫn điện.

-

Chất nền SiCĐiện trở suất rộng và đồng nhất

Dải điện trở suất khả dụng từ 0,01–10 Ω·cm và độ dày tấm wafer từ 350–650 µm với dung sai ±5% về cả nồng độ pha tạp và độ dày—lý tưởng cho việc chế tạo các thiết bị công suất cao.

-

Chất nền SiCMật độ khuyết tật cực thấp

Mật độ vi ống < 0,1 cm⁻² và mật độ sai lệch mặt phẳng đáy < 500 cm⁻², mang lại hiệu suất thiết bị > 99% và độ bền tinh thể vượt trội.

- Chất nền SiCKhả năng dẫn nhiệt vượt trội

Độ dẫn nhiệt lên đến ~370 W/m·K giúp tản nhiệt hiệu quả, tăng độ tin cậy và mật độ công suất của thiết bị.

-

Chất nền SiCỨng dụng mục tiêu

Các transistor MOSFET SiC, điốt Schottky, mô-đun công suất và thiết bị RF dành cho hệ thống truyền động xe điện, biến tần năng lượng mặt trời, hệ thống truyền động công nghiệp, hệ thống kéo và các thị trường điện tử công suất đòi hỏi cao khác.

Thông số kỹ thuật của tấm wafer SiC loại 4H-N 6 inch | ||

| Tài sản | Loại sản phẩm đạt chuẩn MPD (Z) | Điểm số giả (Điểm D) |

| Cấp | Loại sản phẩm đạt chuẩn MPD (Z) | Điểm số giả (Điểm D) |

| Đường kính | 149,5 mm - 150,0 mm | 149,5 mm - 150,0 mm |

| Đa hình | 4H | 4H |

| Độ dày | 350 µm ± 15 µm | 350 µm ± 25 µm |

| Định hướng tấm bán dẫn | Lệch trục: 4,0° về phía <1120> ± 0,5° | Lệch trục: 4,0° về phía <1120> ± 0,5° |

| Mật độ vi ống | ≤ 0,2 cm² | ≤ 15 cm² |

| Điện trở suất | 0,015 - 0,024 Ω·cm | 0,015 - 0,028 Ω·cm |

| Định hướng phẳng chính | [10-10] ± 50° | [10-10] ± 50° |

| Chiều dài phẳng chính | 475 mm ± 2,0 mm | 475 mm ± 2,0 mm |

| Loại trừ cạnh | 3 mm | 3 mm |

| LTV/TIV / Cung / Biến dạng | 2,5 µm / 6 µm / 25 µm / ≤ 35 µm | 5 µm / 15 µm / 40 µm / 60 µm |

| Độ nhám | Độ nhám bề mặt Ba Lan Ra ≤ 1 nm | Độ nhám bề mặt Ba Lan Ra ≤ 1 nm |

| CMP Ra | ≤ 0,2 nm | ≤ 0,5 nm |

| Các vết nứt ở cạnh do ánh sáng cường độ cao | Tổng chiều dài ≤ 20 mm, chiều dài từng đoạn ≤ 2 mm | Tổng chiều dài ≤ 20 mm, chiều dài từng đoạn ≤ 2 mm |

| Tấm lục giác bằng ánh sáng cường độ cao | Diện tích tích lũy ≤ 0,05% | Diện tích tích lũy ≤ 0,1% |

| Các vùng đa dạng cấu trúc bằng ánh sáng cường độ cao | Diện tích tích lũy ≤ 0,05% | Tổng diện tích tích lũy ≤ 3% |

| Các tạp chất cacbon có thể nhìn thấy | Diện tích tích lũy ≤ 0,05% | Tổng diện tích tích lũy ≤ 5% |

| Bề mặt silicon bị trầy xước do ánh sáng cường độ cao. | Tổng chiều dài ≤ 1 đường kính tấm wafer | |

| Phá hủy các chip cạnh bằng ánh sáng cường độ cao | Không cho phép kích thước có chiều rộng và chiều sâu ≥ 0,2 mm. | 7 cái được phép, mỗi cái ≤ 1 mm |

| Trật ren vít | < 500 cm³ | < 500 cm³ |

| Sự nhiễm bẩn bề mặt silicon do ánh sáng cường độ cao | ||

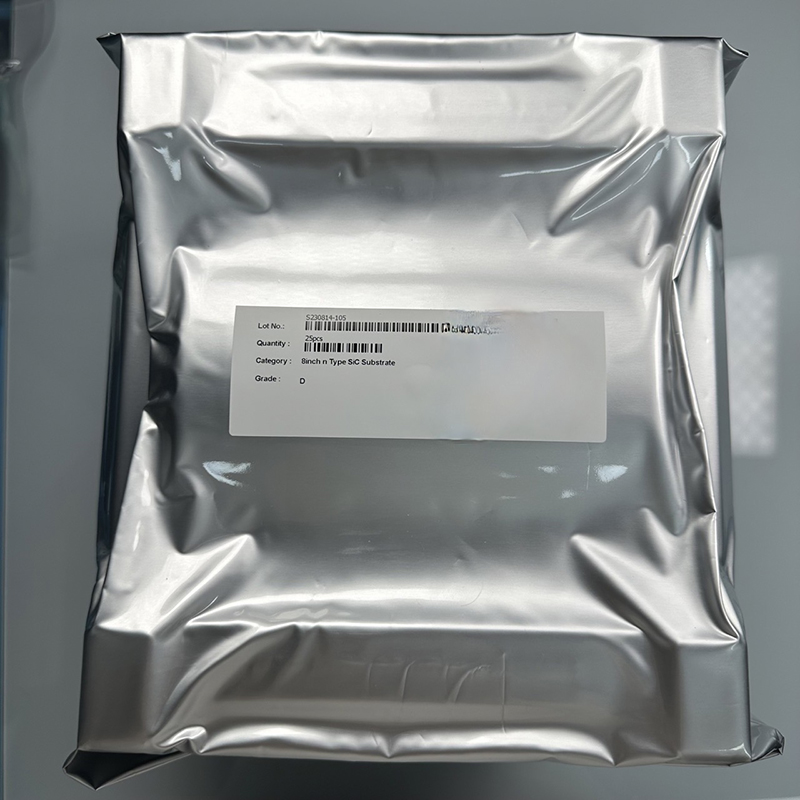

| Bao bì | Khay chứa nhiều tấm wafer hoặc hộp chứa một tấm wafer | Khay chứa nhiều tấm wafer hoặc hộp chứa một tấm wafer |

Thông số kỹ thuật của tấm wafer SiC loại 4H-N 8 inch | ||

| Tài sản | Loại sản phẩm đạt chuẩn MPD (Z) | Điểm số giả (Điểm D) |

| Cấp | Loại sản phẩm đạt chuẩn MPD (Z) | Điểm số giả (Điểm D) |

| Đường kính | 199,5 mm - 200,0 mm | 199,5 mm - 200,0 mm |

| Đa hình | 4H | 4H |

| Độ dày | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Định hướng tấm bán dẫn | 4,0° về phía <110> ± 0,5° | 4,0° về phía <110> ± 0,5° |

| Mật độ vi ống | ≤ 0,2 cm² | ≤ 5 cm² |

| Điện trở suất | 0,015 - 0,025 Ω·cm | 0,015 - 0,028 Ω·cm |

| Định hướng cao quý | ||

| Loại trừ cạnh | 3 mm | 3 mm |

| LTV/TIV / Cung / Biến dạng | 5 µm / 15 µm / 35 µm / 70 µm | 5 µm / 15 µm / 35 µm / 100 µm |

| Độ nhám | Độ nhám bề mặt Ba Lan Ra ≤ 1 nm | Độ nhám bề mặt Ba Lan Ra ≤ 1 nm |

| CMP Ra | ≤ 0,2 nm | ≤ 0,5 nm |

| Các vết nứt ở cạnh do ánh sáng cường độ cao | Tổng chiều dài ≤ 20 mm, chiều dài từng đoạn ≤ 2 mm | Tổng chiều dài ≤ 20 mm, chiều dài từng đoạn ≤ 2 mm |

| Tấm lục giác bằng ánh sáng cường độ cao | Diện tích tích lũy ≤ 0,05% | Diện tích tích lũy ≤ 0,1% |

| Các vùng đa dạng cấu trúc bằng ánh sáng cường độ cao | Diện tích tích lũy ≤ 0,05% | Tổng diện tích tích lũy ≤ 3% |

| Các tạp chất cacbon có thể nhìn thấy | Diện tích tích lũy ≤ 0,05% | Tổng diện tích tích lũy ≤ 5% |

| Bề mặt silicon bị trầy xước do ánh sáng cường độ cao. | Tổng chiều dài ≤ 1 đường kính tấm wafer | |

| Phá hủy các chip cạnh bằng ánh sáng cường độ cao | Không cho phép kích thước có chiều rộng và chiều sâu ≥ 0,2 mm. | 7 cái được phép, mỗi cái ≤ 1 mm |

| Trật ren vít | < 500 cm³ | < 500 cm³ |

| Sự nhiễm bẩn bề mặt silicon do ánh sáng cường độ cao | ||

| Bao bì | Khay chứa nhiều tấm wafer hoặc hộp chứa một tấm wafer | Khay chứa nhiều tấm wafer hoặc hộp chứa một tấm wafer |

4H-SiC là vật liệu hiệu năng cao được sử dụng trong điện tử công suất, thiết bị RF và các ứng dụng nhiệt độ cao. Ký hiệu "4H" đề cập đến cấu trúc tinh thể, là cấu trúc lục giác, và "N" biểu thị loại pha tạp được sử dụng để tối ưu hóa hiệu năng của vật liệu.

Cái4H-SiCLoại này thường được sử dụng cho:

Điện tử công suất:Được sử dụng trong các thiết bị như điốt, MOSFET và IGBT cho hệ thống truyền động xe điện, máy móc công nghiệp và hệ thống năng lượng tái tạo.

Công nghệ 5G:Với nhu cầu về các linh kiện tần số cao và hiệu suất cao của công nghệ 5G, khả năng chịu được điện áp cao và hoạt động ở nhiệt độ cao của SiC khiến nó trở nên lý tưởng cho các bộ khuếch đại công suất trạm gốc và các thiết bị RF.

Hệ thống năng lượng mặt trời:Đặc tính xử lý công suất tuyệt vời của SiC rất lý tưởng cho các bộ biến tần và bộ chuyển đổi quang điện (năng lượng mặt trời).

Xe điện (EV):SiC được sử dụng rộng rãi trong hệ thống truyền động xe điện để chuyển đổi năng lượng hiệu quả hơn, giảm sinh nhiệt và tăng mật độ công suất.

Tính chất và ứng dụng của chất nền SiC loại bán cách điện 4H.

Của cải:

-

Kỹ thuật kiểm soát mật độ không cần ống dẫn siêu nhỏĐảm bảo không có các ống nhỏ li ti, cải thiện chất lượng bề mặt nền.

-

Kỹ thuật điều khiển đơn tinh thểĐảm bảo cấu trúc tinh thể đơn nhất, giúp nâng cao các đặc tính vật liệu.

-

Kỹ thuật kiểm soát tạp chấtGiảm thiểu sự hiện diện của tạp chất hoặc các chất lẫn trong đó, đảm bảo chất nền tinh khiết.

-

Các kỹ thuật kiểm soát điện trở suấtCho phép kiểm soát chính xác điện trở suất, điều này rất quan trọng đối với hiệu suất của thiết bị.

-

Kỹ thuật điều chỉnh và kiểm soát tạp chất: Điều chỉnh và hạn chế sự xâm nhập của tạp chất để duy trì tính toàn vẹn của chất nền.

-

Kỹ thuật kiểm soát độ rộng bước của chất nềnCung cấp khả năng kiểm soát chính xác độ rộng bước, đảm bảo tính nhất quán trên toàn bộ bề mặt vật liệu.

Thông số kỹ thuật đế SiC 4H-semi 6 inch | ||

| Tài sản | Loại sản phẩm đạt chuẩn MPD (Z) | Điểm số giả (Điểm D) |

| Đường kính (mm) | 145 mm - 150 mm | 145 mm - 150 mm |

| Đa hình | 4H | 4H |

| Độ dày (µm) | 500 ± 15 | 500 ± 25 |

| Định hướng tấm bán dẫn | Trên trục: ±0,0001° | Trên trục: ±0,05° |

| Mật độ vi ống | ≤ 15 cm-2 | ≤ 15 cm-2 |

| Điện trở suất (Ωcm) | ≥ 10E3 | ≥ 10E3 |

| Định hướng phẳng chính | (0-10)° ± 5,0° | (10-10)° ± 5,0° |

| Chiều dài phẳng chính | Vết khuyết | Vết khuyết |

| Loại trừ cạnh (mm) | ≤ 2,5 µm / ≤ 15 µm | ≤ 5,5 µm / ≤ 35 µm |

| LTV / Bowl / Warp | ≤ 3 µm | ≤ 3 µm |

| Độ nhám | Độ nhám bề mặt Ba Lan Ra ≤ 1,5 µm | Độ nhám bề mặt Ba Lan Ra ≤ 1,5 µm |

| Phá hủy các chip cạnh bằng ánh sáng cường độ cao | ≤ 20 µm | ≤ 60 µm |

| Tấm gia nhiệt bằng ánh sáng cường độ cao | Tổng cộng ≤ 0,05% | Tổng cộng ≤ 3% |

| Các vùng đa dạng cấu trúc bằng ánh sáng cường độ cao | Hàm lượng tạp chất cacbon có thể nhìn thấy bằng mắt thường ≤ 0,05% | Tổng cộng ≤ 3% |

| Bề mặt silicon bị trầy xước do ánh sáng cường độ cao. | ≤ 0,05% | Tổng cộng ≤ 4% |

| Vết sứt cạnh do ánh sáng cường độ cao (Kích thước) | Không được phép > Chiều rộng và chiều sâu 0,02 mm | Không được phép > Chiều rộng và chiều sâu 0,02 mm |

| Phương pháp giãn nở vít hỗ trợ | ≤ 500 µm | ≤ 500 µm |

| Sự nhiễm bẩn bề mặt silicon do ánh sáng cường độ cao | ≤ 1 x 10^5 | ≤ 1 x 10^5 |

| Bao bì | Khay chứa nhiều tấm wafer hoặc hộp chứa một tấm wafer | Khay chứa nhiều tấm wafer hoặc hộp chứa một tấm wafer |

Thông số kỹ thuật chất nền SiC bán cách điện 4 inch 4H

| Tham số | Loại sản phẩm đạt chuẩn MPD (Z) | Điểm số giả (Điểm D) |

|---|---|---|

| Tính chất vật lý | ||

| Đường kính | 99,5 mm – 100,0 mm | 99,5 mm – 100,0 mm |

| Đa hình | 4H | 4H |

| Độ dày | 500 μm ± 15 μm | 500 μm ± 25 μm |

| Định hướng tấm bán dẫn | Trên trục: <600h > 0,5° | Trên trục: <000h > 0,5° |

| Tính chất điện | ||

| Mật độ vi ống (MPD) | ≤1 cm⁻² | ≤15 cm⁻² |

| Điện trở suất | ≥150 Ω·cm | ≥1,5 Ω·cm |

| Dung sai hình học | ||

| Định hướng phẳng chính | (0x10) ± 5,0° | (0x10) ± 5,0° |

| Chiều dài phẳng chính | 52,5 mm ± 2,0 mm | 52,5 mm ± 2,0 mm |

| Chiều dài phẳng thứ cấp | 18,0 mm ± 2,0 mm | 18,0 mm ± 2,0 mm |

| Định hướng phẳng thứ cấp | 90° theo chiều kim đồng hồ so với mặt phẳng chính ± 5,0° (mặt Si hướng lên) | 90° theo chiều kim đồng hồ so với mặt phẳng chính ± 5,0° (mặt Si hướng lên) |

| Loại trừ cạnh | 3 mm | 3 mm |

| LTV / TTV / Bow / Warp | 2,5 μm / 5 μm / 15 μm / 30 μm | 10 μm / 15 μm / 25 μm / 40 μm |

| Chất lượng bề mặt | ||

| Độ nhám bề mặt (Độ bóng Ra) | ≤1 nm | ≤1 nm |

| Độ nhám bề mặt (CMP Ra) | ≤0,2 nm | ≤0,2 nm |

| Các vết nứt ở cạnh (Ánh sáng cường độ cao) | Không được phép | Tổng chiều dài vết nứt ≥10 mm, vết nứt đơn ≤2 mm |

| Các khuyết tật dạng tấm lục giác | Diện tích tích lũy ≤0,05% | Diện tích tích lũy ≤0,1% |

| Các khu vực bao gồm đa hình | Không được phép | Diện tích tích lũy ≤1% |

| Các tạp chất cacbon có thể nhìn thấy | Diện tích tích lũy ≤0,05% | Diện tích tích lũy ≤1% |

| Vết xước trên bề mặt silicon | Không được phép | Chiều dài tích lũy ≤1 đường kính tấm wafer |

| Mảnh vụn cạnh | Không được phép (chiều rộng/chiều sâu ≥0,2 mm) | ≤5 chip (mỗi chip ≤1 mm) |

| Sự nhiễm bẩn bề mặt silicon | Không được chỉ định | Không được chỉ định |

| Bao bì | ||

| Bao bì | Khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer | Khay chứa nhiều tấm wafer hoặc |

Ứng dụng:

CáiChất nền bán cách điện SiC 4HChúng chủ yếu được sử dụng trong các thiết bị điện tử công suất cao và tần số cao, đặc biệt là trong...trường RFCác chất nền này rất quan trọng đối với nhiều ứng dụng khác nhau, bao gồm:hệ thống thông tin liên lạc vi sóng, radar mảng pha, Vàmáy dò điện không dâyĐộ dẫn nhiệt cao và đặc tính điện tuyệt vời khiến chúng trở nên lý tưởng cho các ứng dụng đòi hỏi khắt khe trong điện tử công suất và hệ thống truyền thông.

Tính chất và ứng dụng của tấm wafer SiC epitaxy loại 4H-N

Tính chất và ứng dụng của tấm bán dẫn SiC loại 4H-N

Tính chất của tấm bán dẫn SiC loại 4H-N:

Thành phần vật liệu:

SiC (Silic cacbua)Được biết đến với độ cứng vượt trội, độ dẫn nhiệt cao và các đặc tính điện tuyệt vời, SiC là vật liệu lý tưởng cho các thiết bị điện tử hiệu suất cao.

Dạng đa hình 4H-SiCDạng thù hình 4H-SiC nổi tiếng với hiệu suất cao và độ ổn định trong các ứng dụng điện tử.

Pha tạp loại N: Pha tạp loại N (pha tạp nitơ) mang lại khả năng di chuyển điện tử tuyệt vời, giúp SiC phù hợp cho các ứng dụng tần số cao và công suất cao.

Độ dẫn nhiệt cao:

Các tấm wafer SiC có độ dẫn nhiệt vượt trội, thường nằm trong khoảng từ120–200 W/m·KĐiều này cho phép chúng quản lý nhiệt hiệu quả trong các thiết bị công suất cao như bóng bán dẫn và điốt.

Khoảng cách băng thông rộng:

Với khe năng lượng là3,26 eV, 4H-SiC có thể hoạt động ở điện áp, tần số và nhiệt độ cao hơn so với các thiết bị dựa trên silicon truyền thống, làm cho nó trở nên lý tưởng cho các ứng dụng hiệu suất cao, tiết kiệm năng lượng.

Tính chất điện:

Độ linh động điện tử và độ dẫn điện cao của SiC khiến nó trở nên lý tưởng cho...điện tử công suấtCung cấp tốc độ chuyển mạch nhanh và khả năng xử lý dòng điện và điện áp cao, giúp hệ thống quản lý năng lượng hiệu quả hơn.

Khả năng chống chịu cơ học và hóa học:

SiC là một trong những vật liệu cứng nhất, chỉ đứng sau kim cương, và có khả năng chống oxy hóa và ăn mòn cao, giúp nó bền bỉ trong môi trường khắc nghiệt.

Ứng dụng của tấm bán dẫn SiC loại 4H-N:

Điện tử công suất:

Các tấm bán dẫn SiC loại 4H-N được sử dụng rộng rãi trongMOSFET công suất, IGBT, Vàđiốtvìchuyển đổi năng lượngtrong các hệ thống nhưbiến tần năng lượng mặt trời, xe điện, Vàhệ thống lưu trữ năng lượng, mang lại hiệu suất và khả năng tiết kiệm năng lượng được nâng cao.

Xe điện (EV):

In hệ thống truyền động xe điện, bộ điều khiển động cơ, Vàtrạm sạcCác tấm wafer SiC giúp đạt được hiệu suất pin tốt hơn, sạc nhanh hơn và cải thiện hiệu năng tổng thể nhờ khả năng chịu được công suất và nhiệt độ cao.

Hệ thống năng lượng tái tạo:

Biến tần năng lượng mặt trời: Các tấm wafer SiC được sử dụng tronghệ thống năng lượng mặt trờiDùng để chuyển đổi nguồn điện một chiều (DC) từ các tấm pin mặt trời thành nguồn điện xoay chiều (AC), giúp tăng hiệu suất và năng suất tổng thể của hệ thống.

Tuabin gióCông nghệ SiC được sử dụng tronghệ thống điều khiển tuabin gióTối ưu hóa hiệu suất phát điện và chuyển đổi năng lượng.

Hàng không vũ trụ và quốc phòng:

Các tấm wafer SiC rất lý tưởng để sử dụng trongđiện tử hàng không vũ trụVàứng dụng quân sự, bao gồmhệ thống radarVàthiết bị điện tử vệ tinhTrong đó, khả năng chống bức xạ cao và độ ổn định nhiệt là rất quan trọng.

Ứng dụng trong môi trường nhiệt độ cao và tần số cao:

Các tấm wafer SiC có ưu điểm vượt trội về...điện tử nhiệt độ caođược sử dụng trongđộng cơ máy bay, tàu vũ trụ, Vàhệ thống sưởi công nghiệpVì chúng duy trì hiệu suất trong điều kiện nhiệt độ khắc nghiệt. Ngoài ra, dải năng lượng rộng của chúng cho phép sử dụng trong...ứng dụng tần số caogiốngThiết bị RFVàtruyền thông vi sóng.

| Thông số kỹ thuật trục epitaxy loại N 6 inch | |||

| Tham số | đơn vị | Z-MOS | |

| Kiểu | Độ dẫn điện / Chất pha tạp | - | Loại N / Nitơ |

| Lớp đệm | Độ dày lớp đệm | um | 1 |

| Dung sai độ dày lớp đệm | % | ±20% | |

| Nồng độ lớp đệm | cm-3 | 1.00E+18 | |

| Dung sai nồng độ lớp đệm | % | ±20% | |

| Lớp biểu bì thứ nhất | Độ dày lớp Epi | um | 11,5 |

| Độ đồng đều độ dày lớp Epi | % | ±4% | |

| Dung sai độ dày lớp Epi ((Thông số kỹ thuật- (Tối đa, Tối thiểu)/Thông số kỹ thuật) | % | ±5% | |

| Nồng độ lớp biểu bì | cm-3 | 1E 15~ 1E 18 | |

| Dung sai nồng độ lớp biểu bì | % | 6% | |

| Độ đồng đều nồng độ lớp Epi (σ) /nghĩa là) | % | ≤5% | |

| Độ đồng đều nồng độ lớp Epi <(max-min)/(max+min> | % | ≤ 10% | |

| Hình dạng tấm mỏng epitaxy | Cây cung | um | ≤±20 |

| BIẾN DẠNG | um | ≤30 | |

| TTV | um | ≤ 10 | |

| LTV | um | ≤2 | |

| Đặc điểm chung | Độ dài vết xước | mm | ≤30mm |

| Mảnh vụn cạnh | - | KHÔNG CÓ | |

| Định nghĩa về khuyết tật | ≥97% (Đo bằng 2*2) Các lỗi nghiêm trọng bao gồm: Các lỗi bao gồm Ống nhỏ / Hố lớn, Cà rốt, Hình tam giác | ||

| Ô nhiễm kim loại | nguyên tử/cm² | d f f ll i 5E10 nguyên tử/cm2 (Al, Cr, Fe, Ni, Cu, Zn, (Hg, Na, K, Ti, Ca & Mn) | |

| Bưu kiện | Thông số đóng gói | cái/hộp | khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer |

| Thông số kỹ thuật epitaxy loại N 8 inch | |||

| Tham số | đơn vị | Z-MOS | |

| Kiểu | Độ dẫn điện / Chất pha tạp | - | Loại N / Nitơ |

| Lớp đệm | Độ dày lớp đệm | um | 1 |

| Dung sai độ dày lớp đệm | % | ±20% | |

| Nồng độ lớp đệm | cm-3 | 1.00E+18 | |

| Dung sai nồng độ lớp đệm | % | ±20% | |

| Lớp biểu bì thứ nhất | Độ dày trung bình của các lớp Epi | um | 8~12 |

| Độ đồng đều độ dày lớp Epi (σ/trung bình) | % | ≤2.0 | |

| Dung sai độ dày lớp Epi ((Thông số kỹ thuật - Tối đa, Tối thiểu)/Thông số kỹ thuật) | % | ±6 | |

| Lớp Epi Trung bình Doping | cm-3 | 8E+15 ~2E+16 | |

| Độ đồng đều pha tạp mạng của các lớp Epi (σ/trung bình) | % | ≤5 | |

| Dung sai pha tạp mạng của các lớp Epi ((Thông số kỹ thuật - Tối đa, | % | ± 10,0 | |

| Hình dạng tấm mỏng epitaxy | Mi )/S ) Biến dạng | um | ≤50,0 |

| Cây cung | um | ± 30,0 | |

| TTV | um | ≤ 10,0 | |

| LTV | um | ≤4,0 (10mm×10mm) | |

| Tổng quan Đặc trưng | Vết xước | - | Tổng chiều dài ≤ 1/2 đường kính wafer |

| Mảnh vụn cạnh | - | ≤2 chip, mỗi chip có bán kính ≤1,5mm | |

| Ô nhiễm kim loại trên bề mặt | nguyên tử/cm2 | 5E10 nguyên tử/cm2 (Al, Cr, Fe, Ni, Cu, Zn, (Hg, Na, K, Ti, Ca & Mn) | |

| Kiểm tra lỗi | % | ≥ 96,0 (Lỗi 2X2 bao gồm các lỗ nhỏ/lỗ lớn, Cà rốt, Khuyết tật hình tam giác, Sự sụp đổ, Tuyến tính/IGSF-s, BPD) | |

| Ô nhiễm kim loại trên bề mặt | nguyên tử/cm2 | 5E10 nguyên tử/cm2 (Al, Cr, Fe, Ni, Cu, Zn, (Hg, Na, K, Ti, Ca & Mn) | |

| Bưu kiện | Thông số đóng gói | - | khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer |

Hỏi đáp về tấm wafer SiC

Câu 1: Những ưu điểm chính của việc sử dụng tấm wafer SiC so với tấm wafer silicon truyền thống trong lĩnh vực điện tử công suất là gì?

A1:

Các tấm wafer SiC mang lại một số ưu điểm quan trọng so với các tấm wafer silicon (Si) truyền thống trong lĩnh vực điện tử công suất, bao gồm:

Hiệu quả cao hơnSiC có dải năng lượng rộng hơn (3,26 eV) so với silicon (1,1 eV), cho phép các thiết bị hoạt động ở điện áp, tần số và nhiệt độ cao hơn. Điều này dẫn đến tổn thất điện năng thấp hơn và hiệu suất cao hơn trong các hệ thống chuyển đổi năng lượng.

Độ dẫn nhiệt caoĐộ dẫn nhiệt của SiC cao hơn nhiều so với silicon, cho phép tản nhiệt tốt hơn trong các ứng dụng công suất cao, giúp cải thiện độ tin cậy và tuổi thọ của các thiết bị điện.

Xử lý điện áp và dòng điện cao hơnCác thiết bị SiC có thể chịu được mức điện áp và dòng điện cao hơn, do đó phù hợp với các ứng dụng công suất cao như xe điện, hệ thống năng lượng tái tạo và bộ điều khiển động cơ công nghiệp.

Tốc độ chuyển mạch nhanh hơnCác thiết bị SiC có khả năng chuyển mạch nhanh hơn, góp phần giảm tổn thất năng lượng và kích thước hệ thống, khiến chúng trở nên lý tưởng cho các ứng dụng tần số cao.

Câu 2: Các ứng dụng chính của tấm wafer SiC trong ngành công nghiệp ô tô là gì?

A2:

Trong ngành công nghiệp ô tô, tấm wafer SiC chủ yếu được sử dụng trong:

Hệ thống truyền động xe điện (EV): Các linh kiện dựa trên SiC nhưbiến tầnVàMOSFET công suấtCải thiện hiệu quả và hiệu suất của hệ thống truyền động xe điện bằng cách cho phép tốc độ chuyển mạch nhanh hơn và mật độ năng lượng cao hơn. Điều này dẫn đến tuổi thọ pin dài hơn và hiệu suất tổng thể của xe tốt hơn.

Bộ sạc trên xeCác thiết bị SiC giúp cải thiện hiệu quả của hệ thống sạc trên xe bằng cách cho phép thời gian sạc nhanh hơn và quản lý nhiệt tốt hơn, điều này rất quan trọng đối với xe điện để hỗ trợ các trạm sạc công suất cao.

Hệ thống quản lý pin (BMS)Công nghệ SiC giúp cải thiện hiệu quả của...hệ thống quản lý pin, cho phép điều chỉnh điện áp tốt hơn, khả năng xử lý công suất cao hơn và tuổi thọ pin dài hơn.

Bộ chuyển đổi DC-DC: Các tấm wafer SiC được sử dụng trongBộ chuyển đổi DC-DCGiúp chuyển đổi nguồn điện một chiều cao áp thành nguồn điện một chiều thấp áp hiệu quả hơn, điều này rất quan trọng trong xe điện để quản lý nguồn điện từ pin đến các bộ phận khác nhau trong xe.

Hiệu năng vượt trội của SiC trong các ứng dụng điện áp cao, nhiệt độ cao và hiệu suất cao khiến nó trở nên thiết yếu cho quá trình chuyển đổi sang xe điện của ngành công nghiệp ô tô.

Thông số kỹ thuật của tấm wafer SiC loại 4H-N 6 inch | ||

| Tài sản | Loại sản phẩm đạt chuẩn MPD (Z) | Điểm số giả (Điểm D) |

| Cấp | Loại sản phẩm đạt chuẩn MPD (Z) | Điểm số giả (Điểm D) |

| Đường kính | 149,5 mm – 150,0 mm | 149,5 mm – 150,0 mm |

| Đa hình | 4H | 4H |

| Độ dày | 350 µm ± 15 µm | 350 µm ± 25 µm |

| Định hướng tấm bán dẫn | Lệch trục: 4,0° về phía <1120> ± 0,5° | Lệch trục: 4,0° về phía <1120> ± 0,5° |

| Mật độ vi ống | ≤ 0,2 cm² | ≤ 15 cm² |

| Điện trở suất | 0,015 – 0,024 Ω·cm | 0,015 – 0,028 Ω·cm |

| Định hướng phẳng chính | [10-10] ± 50° | [10-10] ± 50° |

| Chiều dài phẳng chính | 475 mm ± 2,0 mm | 475 mm ± 2,0 mm |

| Loại trừ cạnh | 3 mm | 3 mm |

| LTV/TIV / Cung / Biến dạng | 2,5 µm / 6 µm / 25 µm / ≤ 35 µm | 5 µm / 15 µm / 40 µm / 60 µm |

| Độ nhám | Độ nhám bề mặt Ba Lan Ra ≤ 1 nm | Độ nhám bề mặt Ba Lan Ra ≤ 1 nm |

| CMP Ra | ≤ 0,2 nm | ≤ 0,5 nm |

| Các vết nứt ở cạnh do ánh sáng cường độ cao | Tổng chiều dài ≤ 20 mm, chiều dài từng đoạn ≤ 2 mm | Tổng chiều dài ≤ 20 mm, chiều dài từng đoạn ≤ 2 mm |

| Tấm lục giác bằng ánh sáng cường độ cao | Diện tích tích lũy ≤ 0,05% | Diện tích tích lũy ≤ 0,1% |

| Các vùng đa dạng cấu trúc bằng ánh sáng cường độ cao | Diện tích tích lũy ≤ 0,05% | Tổng diện tích tích lũy ≤ 3% |

| Các tạp chất cacbon có thể nhìn thấy | Diện tích tích lũy ≤ 0,05% | Tổng diện tích tích lũy ≤ 5% |

| Bề mặt silicon bị trầy xước do ánh sáng cường độ cao. | Tổng chiều dài ≤ 1 đường kính tấm wafer | |

| Phá hủy các chip cạnh bằng ánh sáng cường độ cao | Không cho phép kích thước có chiều rộng và chiều sâu ≥ 0,2 mm. | 7 cái được phép, mỗi cái ≤ 1 mm |

| Trật ren vít | < 500 cm³ | < 500 cm³ |

| Sự nhiễm bẩn bề mặt silicon do ánh sáng cường độ cao | ||

| Bao bì | Khay chứa nhiều tấm wafer hoặc hộp chứa một tấm wafer | Khay chứa nhiều tấm wafer hoặc hộp chứa một tấm wafer |

Thông số kỹ thuật của tấm wafer SiC loại 4H-N 8 inch | ||

| Tài sản | Loại sản phẩm đạt chuẩn MPD (Z) | Điểm số giả (Điểm D) |

| Cấp | Loại sản phẩm đạt chuẩn MPD (Z) | Điểm số giả (Điểm D) |

| Đường kính | 199,5 mm – 200,0 mm | 199,5 mm – 200,0 mm |

| Đa hình | 4H | 4H |

| Độ dày | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Định hướng tấm bán dẫn | 4,0° về phía <110> ± 0,5° | 4,0° về phía <110> ± 0,5° |

| Mật độ vi ống | ≤ 0,2 cm² | ≤ 5 cm² |

| Điện trở suất | 0,015 – 0,025 Ω·cm | 0,015 – 0,028 Ω·cm |

| Định hướng cao quý | ||

| Loại trừ cạnh | 3 mm | 3 mm |

| LTV/TIV / Cung / Biến dạng | 5 µm / 15 µm / 35 µm / 70 µm | 5 µm / 15 µm / 35 µm / 100 µm |

| Độ nhám | Độ nhám bề mặt Ba Lan Ra ≤ 1 nm | Độ nhám bề mặt Ba Lan Ra ≤ 1 nm |

| CMP Ra | ≤ 0,2 nm | ≤ 0,5 nm |

| Các vết nứt ở cạnh do ánh sáng cường độ cao | Tổng chiều dài ≤ 20 mm, chiều dài từng đoạn ≤ 2 mm | Tổng chiều dài ≤ 20 mm, chiều dài từng đoạn ≤ 2 mm |

| Tấm lục giác bằng ánh sáng cường độ cao | Diện tích tích lũy ≤ 0,05% | Diện tích tích lũy ≤ 0,1% |

| Các vùng đa dạng cấu trúc bằng ánh sáng cường độ cao | Diện tích tích lũy ≤ 0,05% | Tổng diện tích tích lũy ≤ 3% |

| Các tạp chất cacbon có thể nhìn thấy | Diện tích tích lũy ≤ 0,05% | Tổng diện tích tích lũy ≤ 5% |

| Bề mặt silicon bị trầy xước do ánh sáng cường độ cao. | Tổng chiều dài ≤ 1 đường kính tấm wafer | |

| Phá hủy các chip cạnh bằng ánh sáng cường độ cao | Không cho phép kích thước có chiều rộng và chiều sâu ≥ 0,2 mm. | 7 cái được phép, mỗi cái ≤ 1 mm |

| Trật ren vít | < 500 cm³ | < 500 cm³ |

| Sự nhiễm bẩn bề mặt silicon do ánh sáng cường độ cao | ||

| Bao bì | Khay chứa nhiều tấm wafer hoặc hộp chứa một tấm wafer | Khay chứa nhiều tấm wafer hoặc hộp chứa một tấm wafer |

Thông số kỹ thuật đế SiC 4H-semi 6 inch | ||

| Tài sản | Loại sản phẩm đạt chuẩn MPD (Z) | Điểm số giả (Điểm D) |

| Đường kính (mm) | 145 mm – 150 mm | 145 mm – 150 mm |

| Đa hình | 4H | 4H |

| Độ dày (µm) | 500 ± 15 | 500 ± 25 |

| Định hướng tấm bán dẫn | Trên trục: ±0,0001° | Trên trục: ±0,05° |

| Mật độ vi ống | ≤ 15 cm-2 | ≤ 15 cm-2 |

| Điện trở suất (Ωcm) | ≥ 10E3 | ≥ 10E3 |

| Định hướng phẳng chính | (0-10)° ± 5,0° | (10-10)° ± 5,0° |

| Chiều dài phẳng chính | Vết khuyết | Vết khuyết |

| Loại trừ cạnh (mm) | ≤ 2,5 µm / ≤ 15 µm | ≤ 5,5 µm / ≤ 35 µm |

| LTV / Bowl / Warp | ≤ 3 µm | ≤ 3 µm |

| Độ nhám | Độ nhám bề mặt Ba Lan Ra ≤ 1,5 µm | Độ nhám bề mặt Ba Lan Ra ≤ 1,5 µm |

| Phá hủy các chip cạnh bằng ánh sáng cường độ cao | ≤ 20 µm | ≤ 60 µm |

| Tấm gia nhiệt bằng ánh sáng cường độ cao | Tổng cộng ≤ 0,05% | Tổng cộng ≤ 3% |

| Các vùng đa dạng cấu trúc bằng ánh sáng cường độ cao | Hàm lượng tạp chất cacbon có thể nhìn thấy bằng mắt thường ≤ 0,05% | Tổng cộng ≤ 3% |

| Bề mặt silicon bị trầy xước do ánh sáng cường độ cao. | ≤ 0,05% | Tổng cộng ≤ 4% |

| Vết sứt cạnh do ánh sáng cường độ cao (Kích thước) | Không được phép > Chiều rộng và chiều sâu 0,02 mm | Không được phép > Chiều rộng và chiều sâu 0,02 mm |

| Phương pháp giãn nở vít hỗ trợ | ≤ 500 µm | ≤ 500 µm |

| Sự nhiễm bẩn bề mặt silicon do ánh sáng cường độ cao | ≤ 1 x 10^5 | ≤ 1 x 10^5 |

| Bao bì | Khay chứa nhiều tấm wafer hoặc hộp chứa một tấm wafer | Khay chứa nhiều tấm wafer hoặc hộp chứa một tấm wafer |

Thông số kỹ thuật chất nền SiC bán cách điện 4 inch 4H

| Tham số | Loại sản phẩm đạt chuẩn MPD (Z) | Điểm số giả (Điểm D) |

|---|---|---|

| Tính chất vật lý | ||

| Đường kính | 99,5 mm – 100,0 mm | 99,5 mm – 100,0 mm |

| Đa hình | 4H | 4H |

| Độ dày | 500 μm ± 15 μm | 500 μm ± 25 μm |

| Định hướng tấm bán dẫn | Trên trục: <600h > 0,5° | Trên trục: <000h > 0,5° |

| Tính chất điện | ||

| Mật độ vi ống (MPD) | ≤1 cm⁻² | ≤15 cm⁻² |

| Điện trở suất | ≥150 Ω·cm | ≥1,5 Ω·cm |

| Dung sai hình học | ||

| Định hướng phẳng chính | (0×10) ± 5,0° | (0×10) ± 5,0° |

| Chiều dài phẳng chính | 52,5 mm ± 2,0 mm | 52,5 mm ± 2,0 mm |

| Chiều dài phẳng thứ cấp | 18,0 mm ± 2,0 mm | 18,0 mm ± 2,0 mm |

| Định hướng phẳng thứ cấp | 90° theo chiều kim đồng hồ so với mặt phẳng chính ± 5,0° (mặt Si hướng lên) | 90° theo chiều kim đồng hồ so với mặt phẳng chính ± 5,0° (mặt Si hướng lên) |

| Loại trừ cạnh | 3 mm | 3 mm |

| LTV / TTV / Bow / Warp | 2,5 μm / 5 μm / 15 μm / 30 μm | 10 μm / 15 μm / 25 μm / 40 μm |

| Chất lượng bề mặt | ||

| Độ nhám bề mặt (Độ bóng Ra) | ≤1 nm | ≤1 nm |

| Độ nhám bề mặt (CMP Ra) | ≤0,2 nm | ≤0,2 nm |

| Các vết nứt ở cạnh (Ánh sáng cường độ cao) | Không được phép | Tổng chiều dài vết nứt ≥10 mm, vết nứt đơn ≤2 mm |

| Các khuyết tật dạng tấm lục giác | Diện tích tích lũy ≤0,05% | Diện tích tích lũy ≤0,1% |

| Các khu vực bao gồm đa hình | Không được phép | Diện tích tích lũy ≤1% |

| Các tạp chất cacbon có thể nhìn thấy | Diện tích tích lũy ≤0,05% | Diện tích tích lũy ≤1% |

| Vết xước trên bề mặt silicon | Không được phép | Chiều dài tích lũy ≤1 đường kính tấm wafer |

| Mảnh vụn cạnh | Không được phép (chiều rộng/chiều sâu ≥0,2 mm) | ≤5 chip (mỗi chip ≤1 mm) |

| Sự nhiễm bẩn bề mặt silicon | Không được chỉ định | Không được chỉ định |

| Bao bì | ||

| Bao bì | Khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer | Khay chứa nhiều tấm wafer hoặc |

| Thông số kỹ thuật trục epitaxy loại N 6 inch | |||

| Tham số | đơn vị | Z-MOS | |

| Kiểu | Độ dẫn điện / Chất pha tạp | - | Loại N / Nitơ |

| Lớp đệm | Độ dày lớp đệm | um | 1 |

| Dung sai độ dày lớp đệm | % | ±20% | |

| Nồng độ lớp đệm | cm-3 | 1.00E+18 | |

| Dung sai nồng độ lớp đệm | % | ±20% | |

| Lớp biểu bì thứ nhất | Độ dày lớp Epi | um | 11,5 |

| Độ đồng đều độ dày lớp Epi | % | ±4% | |

| Dung sai độ dày lớp Epi ((Thông số kỹ thuật- (Tối đa, Tối thiểu)/Thông số kỹ thuật) | % | ±5% | |

| Nồng độ lớp biểu bì | cm-3 | 1E 15~ 1E 18 | |

| Dung sai nồng độ lớp biểu bì | % | 6% | |

| Độ đồng đều nồng độ lớp Epi (σ) /nghĩa là) | % | ≤5% | |

| Độ đồng đều nồng độ lớp Epi <(max-min)/(max+min> | % | ≤ 10% | |

| Hình dạng tấm mỏng epitaxy | Cây cung | um | ≤±20 |

| BIẾN DẠNG | um | ≤30 | |

| TTV | um | ≤ 10 | |

| LTV | um | ≤2 | |

| Đặc điểm chung | Độ dài vết xước | mm | ≤30mm |

| Mảnh vụn cạnh | - | KHÔNG CÓ | |

| Định nghĩa về khuyết tật | ≥97% (Đo bằng 2*2) Các lỗi nghiêm trọng bao gồm: Các lỗi bao gồm Ống nhỏ / Hố lớn, Cà rốt, Hình tam giác | ||

| Ô nhiễm kim loại | nguyên tử/cm² | d f f ll i 5E10 nguyên tử/cm2 (Al, Cr, Fe, Ni, Cu, Zn, (Hg, Na, K, Ti, Ca & Mn) | |

| Bưu kiện | Thông số đóng gói | cái/hộp | khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer |

| Thông số kỹ thuật epitaxy loại N 8 inch | |||

| Tham số | đơn vị | Z-MOS | |

| Kiểu | Độ dẫn điện / Chất pha tạp | - | Loại N / Nitơ |

| Lớp đệm | Độ dày lớp đệm | um | 1 |

| Dung sai độ dày lớp đệm | % | ±20% | |

| Nồng độ lớp đệm | cm-3 | 1.00E+18 | |

| Dung sai nồng độ lớp đệm | % | ±20% | |

| Lớp biểu bì thứ nhất | Độ dày trung bình của các lớp Epi | um | 8~12 |

| Độ đồng đều độ dày lớp Epi (σ/trung bình) | % | ≤2.0 | |

| Dung sai độ dày lớp Epi ((Thông số kỹ thuật - Tối đa, Tối thiểu)/Thông số kỹ thuật) | % | ±6 | |

| Lớp Epi Trung bình Doping | cm-3 | 8E+15 ~2E+16 | |

| Độ đồng đều pha tạp mạng của các lớp Epi (σ/trung bình) | % | ≤5 | |

| Dung sai pha tạp mạng của các lớp Epi ((Thông số kỹ thuật - Tối đa, | % | ± 10,0 | |

| Hình dạng tấm mỏng epitaxy | Mi )/S ) Biến dạng | um | ≤50,0 |

| Cây cung | um | ± 30,0 | |

| TTV | um | ≤ 10,0 | |

| LTV | um | ≤4,0 (10mm×10mm) | |

| Tổng quan Đặc trưng | Vết xước | - | Tổng chiều dài ≤ 1/2 đường kính wafer |

| Mảnh vụn cạnh | - | ≤2 chip, mỗi chip có bán kính ≤1,5mm | |

| Ô nhiễm kim loại trên bề mặt | nguyên tử/cm2 | 5E10 nguyên tử/cm2 (Al, Cr, Fe, Ni, Cu, Zn, (Hg, Na, K, Ti, Ca & Mn) | |

| Kiểm tra lỗi | % | ≥ 96,0 (Lỗi 2X2 bao gồm các lỗ nhỏ/lỗ lớn, Cà rốt, Khuyết tật hình tam giác, Sự sụp đổ, Tuyến tính/IGSF-s, BPD) | |

| Ô nhiễm kim loại trên bề mặt | nguyên tử/cm2 | 5E10 nguyên tử/cm2 (Al, Cr, Fe, Ni, Cu, Zn, (Hg, Na, K, Ti, Ca & Mn) | |

| Bưu kiện | Thông số đóng gói | - | khay chứa nhiều tấm wafer hoặc hộp đựng một tấm wafer |

Câu 1: Những ưu điểm chính của việc sử dụng tấm wafer SiC so với tấm wafer silicon truyền thống trong lĩnh vực điện tử công suất là gì?

A1:

Các tấm wafer SiC mang lại một số ưu điểm quan trọng so với các tấm wafer silicon (Si) truyền thống trong lĩnh vực điện tử công suất, bao gồm:

Hiệu quả cao hơnSiC có dải năng lượng rộng hơn (3,26 eV) so với silicon (1,1 eV), cho phép các thiết bị hoạt động ở điện áp, tần số và nhiệt độ cao hơn. Điều này dẫn đến tổn thất điện năng thấp hơn và hiệu suất cao hơn trong các hệ thống chuyển đổi năng lượng.

Độ dẫn nhiệt caoĐộ dẫn nhiệt của SiC cao hơn nhiều so với silicon, cho phép tản nhiệt tốt hơn trong các ứng dụng công suất cao, giúp cải thiện độ tin cậy và tuổi thọ của các thiết bị điện.

Xử lý điện áp và dòng điện cao hơnCác thiết bị SiC có thể chịu được mức điện áp và dòng điện cao hơn, do đó phù hợp với các ứng dụng công suất cao như xe điện, hệ thống năng lượng tái tạo và bộ điều khiển động cơ công nghiệp.

Tốc độ chuyển mạch nhanh hơnCác thiết bị SiC có khả năng chuyển mạch nhanh hơn, góp phần giảm tổn thất năng lượng và kích thước hệ thống, khiến chúng trở nên lý tưởng cho các ứng dụng tần số cao.

Câu 2: Các ứng dụng chính của tấm wafer SiC trong ngành công nghiệp ô tô là gì?

A2:

Trong ngành công nghiệp ô tô, tấm wafer SiC chủ yếu được sử dụng trong:

Hệ thống truyền động xe điện (EV): Các linh kiện dựa trên SiC nhưbiến tầnVàMOSFET công suấtCải thiện hiệu quả và hiệu suất của hệ thống truyền động xe điện bằng cách cho phép tốc độ chuyển mạch nhanh hơn và mật độ năng lượng cao hơn. Điều này dẫn đến tuổi thọ pin dài hơn và hiệu suất tổng thể của xe tốt hơn.

Bộ sạc trên xeCác thiết bị SiC giúp cải thiện hiệu quả của hệ thống sạc trên xe bằng cách cho phép thời gian sạc nhanh hơn và quản lý nhiệt tốt hơn, điều này rất quan trọng đối với xe điện để hỗ trợ các trạm sạc công suất cao.

Hệ thống quản lý pin (BMS)Công nghệ SiC giúp cải thiện hiệu quả của...hệ thống quản lý pin, cho phép điều chỉnh điện áp tốt hơn, khả năng xử lý công suất cao hơn và tuổi thọ pin dài hơn.

Bộ chuyển đổi DC-DC: Các tấm wafer SiC được sử dụng trongBộ chuyển đổi DC-DCGiúp chuyển đổi nguồn điện một chiều cao áp thành nguồn điện một chiều thấp áp hiệu quả hơn, điều này rất quan trọng trong xe điện để quản lý nguồn điện từ pin đến các bộ phận khác nhau trong xe.

Hiệu năng vượt trội của SiC trong các ứng dụng điện áp cao, nhiệt độ cao và hiệu suất cao khiến nó trở nên thiết yếu cho quá trình chuyển đổi sang xe điện của ngành công nghiệp ô tô.