Tấm wafer SiCOI 4 inch 6 inch HPSI SiC SiO2 Cấu trúc chất nền Si

Cấu trúc của tấm wafer SiCOI

HPB (High-Performance Bonding), BIC (Bonded Integrated Circuit) và SOD (Silicon-on-Diamond hoặc Silicon-on-Insulator-like technology). Nó bao gồm:

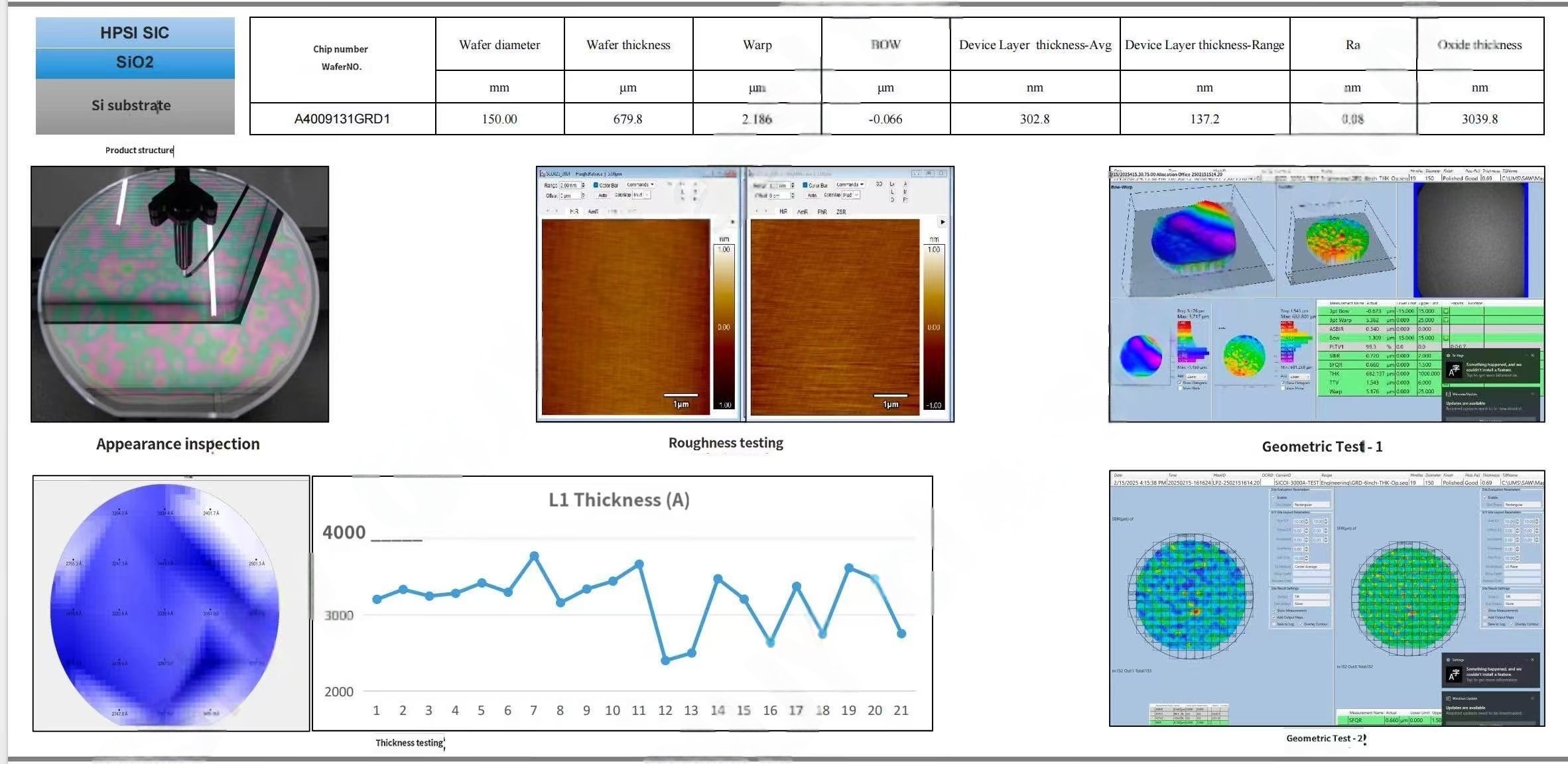

Các chỉ số hiệu suất:

Liệt kê các tham số như độ chính xác, loại lỗi (ví dụ: "Không có lỗi," "Khoảng cách giá trị") và phép đo độ dày (ví dụ: "Độ dày lớp trực tiếp/kg").

Một bảng với các giá trị số (có thể là thông số thí nghiệm hoặc quy trình) dưới các tiêu đề như "ADDR/SYGBDT," "10/0," v.v.

Dữ liệu độ dày lớp:

Các mục lặp đi lặp lại nhiều lần được dán nhãn từ "L1 Độ dày (A)" đến "L270 Độ dày (A)" (có thể tính bằng Ångström, 1 Å = 0,1 nm).

Điều này cho thấy cấu trúc nhiều lớp với khả năng kiểm soát độ dày chính xác cho từng lớp, đặc trưng của các tấm bán dẫn tiên tiến.

Cấu trúc tấm wafer SiCOI

SiCOI (Silicon Carbide on Insulator) là cấu trúc wafer chuyên dụng kết hợp silicon carbide (SiC) với một lớp cách điện, tương tự như SOI (Silicon-on-Insulator) nhưng được tối ưu hóa cho các ứng dụng công suất cao/nhiệt độ cao. Các tính năng chính:

Thành phần lớp:

Lớp trên cùng: Silicon Carbide (SiC) đơn tinh thể cho độ linh động điện tử cao và độ ổn định nhiệt tốt.

Lớp cách điện chôn ngầm: Thường là SiO₂ (oxit) hoặc kim cương (trong SOD) để giảm điện dung ký sinh và cải thiện khả năng cách ly.

Lớp nền: Silicon hoặc SiC đa tinh thể để hỗ trợ cơ học.

Đặc tính của tấm wafer SiCOI

Tính chất điện Dải năng lượng rộng (3,2 eV đối với 4H-SiC): Cho phép điện áp đánh thủng cao (cao hơn silicon hơn 10 lần). Giảm dòng rò rỉ, cải thiện hiệu suất trong các thiết bị điện.

Độ linh động điện tử cao:~900 cm²/V·s (4H-SiC) so với ~1.400 cm²/V·s (Si), nhưng hiệu suất ở điện trường cao tốt hơn.

Điện trở bật thấp:Các transistor dựa trên SiCOI (ví dụ: MOSFET) thể hiện tổn hao dẫn điện thấp hơn.

Khả năng cách nhiệt tuyệt vời:Lớp oxit (SiO₂) hoặc lớp kim cương nằm sâu bên trong giúp giảm thiểu điện dung ký sinh và nhiễu xuyên kênh.

- Tính chất nhiệtĐộ dẫn nhiệt cao: SiC (~490 W/m·K đối với 4H-SiC) so với Si (~150 W/m·K). Kim cương (nếu được sử dụng làm chất cách điện) có thể vượt quá 2.000 W/m·K, giúp tăng cường khả năng tản nhiệt.

Độ ổn định nhiệt:Hoạt động ổn định ở nhiệt độ >300°C (so với ~150°C đối với silicon). Giảm yêu cầu làm mát trong các thiết bị điện tử công suất.

3. Tính chất cơ học và hóa họcĐộ cứng cực cao (~9,5 Mohs): Chống mài mòn, giúp SiCOI bền bỉ trong môi trường khắc nghiệt.

Tính trơ về mặt hóa học:Chống oxy hóa và ăn mòn, ngay cả trong điều kiện axit/kiềm.

Hệ số giãn nở nhiệt thấp:Phù hợp tốt với các vật liệu chịu nhiệt cao khác (ví dụ: GaN).

4. Ưu điểm về cấu trúc (so với SiC khối hoặc SOI)

Giảm thiểu tổn thất chất nền:Lớp cách điện ngăn dòng điện rò rỉ vào chất nền.

Cải thiện hiệu năng RF:Điện dung ký sinh thấp hơn cho phép chuyển mạch nhanh hơn (hữu ích cho các thiết bị 5G/mmWave).

Thiết kế linh hoạt:Lớp SiC mỏng phía trên cho phép tối ưu hóa việc thu nhỏ kích thước thiết bị (ví dụ: các kênh siêu mỏng trong bóng bán dẫn).

So sánh với SOI và SiC khối

| Tài sản | SiCOI | SOI (Si/SiO₂/Si) | SiC khối |

| Khoảng cách băng tần | 3,2 eV (SiC) | 1,1 eV (Si) | 3,2 eV (SiC) |

| Độ dẫn nhiệt | Cao (SiC + kim cương) | Hàm lượng SiO₂ thấp (giới hạn truyền nhiệt) | Cao (chỉ dành cho SiC) |

| Điện áp đánh thủng | Rất cao | Vừa phải | Rất cao |

| Trị giá | Cao hơn | Thấp hơn | Cao nhất (SiC nguyên chất) |

Ứng dụng của tấm wafer SiCOI

Điện tử công suất

Các tấm wafer SiCOI được sử dụng rộng rãi trong các thiết bị bán dẫn điện áp cao và công suất cao như MOSFET, điốt Schottky và công tắc nguồn. Vùng cấm rộng và điện áp đánh thủng cao của SiC cho phép chuyển đổi năng lượng hiệu quả với tổn thất giảm và hiệu suất tản nhiệt được nâng cao.

Thiết bị tần số vô tuyến (RF)

Lớp cách điện trong các tấm wafer SiCOI làm giảm điện dung ký sinh, giúp chúng phù hợp cho các bóng bán dẫn và bộ khuếch đại tần số cao được sử dụng trong viễn thông, radar và công nghệ 5G.

Hệ thống vi cơ điện tử (MEMS)

Các tấm wafer SiCOI cung cấp một nền tảng vững chắc để chế tạo các cảm biến và bộ truyền động MEMS hoạt động đáng tin cậy trong môi trường khắc nghiệt nhờ tính trơ về mặt hóa học và độ bền cơ học của SiC.

Điện tử chịu nhiệt độ cao

SiCOI cho phép tạo ra các thiết bị điện tử duy trì hiệu suất và độ tin cậy ở nhiệt độ cao, mang lại lợi ích cho các ứng dụng trong ngành ô tô, hàng không vũ trụ và công nghiệp, nơi các thiết bị silicon thông thường không thể hoạt động.

Thiết bị quang tử và quang điện tử

Sự kết hợp giữa các đặc tính quang học của SiC và lớp cách điện tạo điều kiện thuận lợi cho việc tích hợp các mạch quang tử với khả năng quản lý nhiệt được cải thiện.

Thiết bị điện tử chống bức xạ

Nhờ khả năng chịu bức xạ vốn có của SiC, các tấm wafer SiCOI rất lý tưởng cho các ứng dụng trong không gian và hạt nhân, đòi hỏi các thiết bị có thể chịu được môi trường bức xạ cao.

Hỏi đáp về tấm wafer SiCOI

Câu 1: Tấm wafer SiCOI là gì?

A: SiCOI là viết tắt của Silicon Carbide-on-Insulator (Cabinyl Cacbua trên chất cách điện). Đây là cấu trúc tấm bán dẫn trong đó một lớp mỏng cacbua silic (SiC) được liên kết với một lớp cách điện (thường là silic dioxit, SiO₂), được đỡ bởi một chất nền silic. Cấu trúc này kết hợp các đặc tính tuyệt vời của SiC với khả năng cách điện khỏi chất cách điện.

Câu 2: Những ưu điểm chính của tấm wafer SiCOI là gì?

A: Những ưu điểm chính bao gồm điện áp đánh thủng cao, dải năng lượng rộng, độ dẫn nhiệt tuyệt vời, độ cứng cơ học vượt trội và điện dung ký sinh giảm nhờ lớp cách điện. Điều này dẫn đến hiệu suất, hiệu quả và độ tin cậy được cải thiện của thiết bị.

Câu 3: Các ứng dụng điển hình của tấm wafer SiCOI là gì?

A: Chúng được sử dụng trong điện tử công suất, thiết bị RF tần số cao, cảm biến MEMS, điện tử chịu nhiệt độ cao, thiết bị quang tử và điện tử chống bức xạ.

Sơ đồ chi tiết