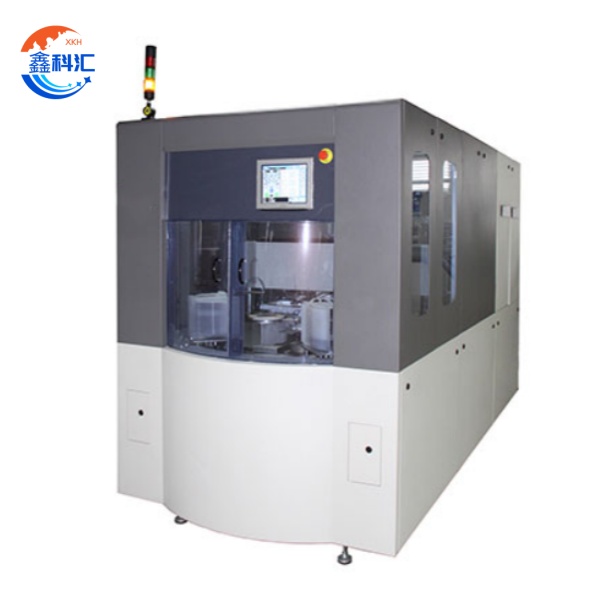

Thiết bị làm mỏng wafer cho quá trình xử lý wafer sapphire/SiC/Si từ 4 inch đến 12 inch.

Nguyên lý hoạt động

Quá trình làm mỏng tấm bán dẫn diễn ra qua ba giai đoạn:

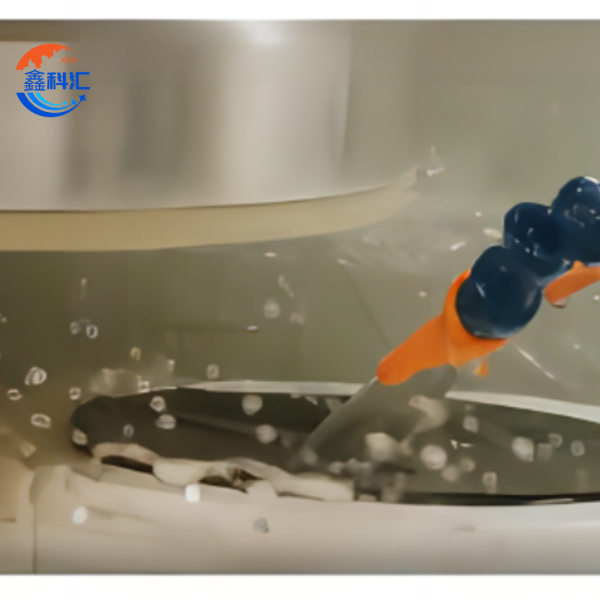

Mài thô: Đá mài kim cương (kích thước hạt 200–500 μm) loại bỏ 50–150 μm vật liệu ở tốc độ 3000–5000 vòng/phút để giảm độ dày nhanh chóng.

Mài mịn: Sử dụng đá mài mịn hơn (kích thước hạt 1–50 μm) sẽ giảm độ dày xuống còn 20–50 μm với tốc độ <1 μm/s để giảm thiểu hư hại dưới bề mặt.

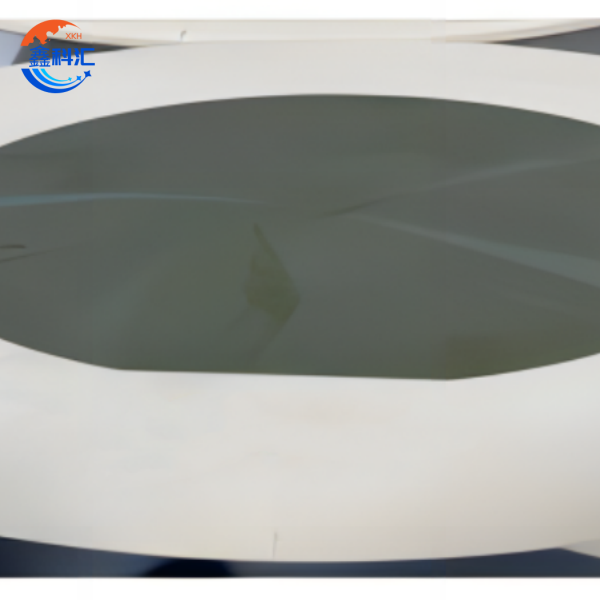

Đánh bóng (CMP): Dung dịch đánh bóng hóa học-cơ học loại bỏ các hư hại còn sót lại, đạt được độ nhám bề mặt Ra <0,1 nm.

Vật liệu tương thích

Silicon (Si): Vật liệu tiêu chuẩn cho các tấm wafer CMOS, được làm mỏng đến 25 μm để xếp chồng 3D.

Silicon Carbide (SiC): Cần sử dụng đá mài kim cương chuyên dụng (nồng độ kim cương 80%) để đảm bảo độ ổn định nhiệt.

Sapphire (Al₂O₃): Được làm mỏng đến 50 μm để ứng dụng trong đèn LED UV.

Các thành phần cốt lõi của hệ thống

1. Hệ thống nghiền

Máy mài hai trục: Kết hợp mài thô/mịn trên cùng một thiết bị, giảm thời gian chu kỳ đến 40%.

Trục chính khí nén: Phạm vi tốc độ 0–6000 vòng/phút với độ lệch tâm xuyên tâm <0,5 μm.

2. Hệ thống xử lý wafer

Mâm cặp hút chân không: Lực giữ >50 N với độ chính xác định vị ±0,1 μm.

Cánh tay robot: Vận chuyển các tấm wafer có kích thước từ 4 đến 12 inch với tốc độ 100 mm/giây.

3. Hệ thống điều khiển

Giao thoa kế laser: Giám sát độ dày theo thời gian thực (độ phân giải 0,01 μm).

Công nghệ phản hồi dựa trên AI: Dự đoán độ mòn của bánh xe và tự động điều chỉnh các thông số.

4. Làm mát & Vệ sinh

Làm sạch bằng sóng siêu âm: Loại bỏ các hạt có kích thước >0,5 μm với hiệu quả 99,9%.

Nước khử ion: Làm mát tấm bán dẫn xuống dưới 5°C so với nhiệt độ môi trường.

Lợi thế cốt lõi

1. Độ chính xác cực cao: TTV (Tổng độ biến thiên độ dày) <0,5 μm, WTW (Độ biến thiên độ dày trong cùng một tấm wafer) <1 μm.

2. Tích hợp đa quy trình: Kết hợp mài, đánh bóng hóa học cơ học (CMP) và khắc plasma trong cùng một máy.

3. Khả năng tương thích vật liệu:

Silicon: Độ dày giảm từ 775 μm xuống còn 25 μm.

SiC: Đạt được TTV <2 μm cho các ứng dụng RF.

Các tấm wafer pha tạp: Các tấm wafer InP pha tạp phốt pho với độ biến thiên điện trở suất <5%.

4. Tự động hóa thông minh: Tích hợp MES giúp giảm lỗi do con người đến 70%.

5. Hiệu quả năng lượng: Tiết kiệm 30% điện năng nhờ hệ thống phanh tái tạo năng lượng.

Các ứng dụng chính

1. Bao bì tiên tiến

• IC 3D: Việc làm mỏng tấm wafer cho phép xếp chồng các chip logic/bộ nhớ theo chiều dọc (ví dụ: các chồng HBM), đạt được băng thông cao hơn gấp 10 lần và giảm 50% mức tiêu thụ điện năng so với các giải pháp 2.5D. Thiết bị hỗ trợ liên kết lai và tích hợp TSV (Through-Silicon Via), rất quan trọng đối với các bộ xử lý AI/ML yêu cầu khoảng cách kết nối <10 μm. Ví dụ, các tấm wafer 12 inch được làm mỏng xuống còn 25 μm cho phép xếp chồng hơn 8 lớp trong khi vẫn duy trì độ cong vênh <1,5%, điều cần thiết cho các hệ thống LiDAR ô tô.

• Công nghệ đóng gói Fan-Out: Bằng cách giảm độ dày wafer xuống 30 μm, chiều dài kết nối được rút ngắn 50%, giảm thiểu độ trễ tín hiệu (<0,2 ps/mm) và cho phép tạo ra các chiplet siêu mỏng 0,4 mm cho SoC di động. Quy trình này tận dụng các thuật toán mài bù ứng suất để ngăn ngừa biến dạng (kiểm soát TTV >50 μm), đảm bảo độ tin cậy trong các ứng dụng RF tần số cao.

2. Điện tử công suất

• Mô-đun IGBT: Làm mỏng đến 50 μm giúp giảm điện trở nhiệt xuống <0,5°C/W, cho phép MOSFET SiC 1200V hoạt động ở nhiệt độ mối nối 200°C. Thiết bị của chúng tôi sử dụng quy trình mài nhiều giai đoạn (thô: hạt mài 46 μm → mịn: hạt mài 4 μm) để loại bỏ hư hỏng dưới bề mặt, đạt được độ tin cậy chu kỳ nhiệt >10.000 chu kỳ. Điều này rất quan trọng đối với bộ biến tần xe điện, nơi các tấm wafer SiC dày 10 μm giúp cải thiện tốc độ chuyển mạch lên 30%.

• Thiết bị công suất GaN trên SiC: Làm mỏng tấm wafer xuống 80 μm giúp tăng cường độ linh động của electron (μ > 2000 cm²/V·s) cho các transistor GaN HEMT 650V, giảm tổn thất dẫn điện 18%. Quy trình này sử dụng phương pháp cắt bằng laser để ngăn ngừa nứt vỡ trong quá trình làm mỏng, đạt được độ dày mảnh vỡ cạnh <5 μm cho các bộ khuếch đại công suất RF.

3. Quang điện tử

• Đèn LED GaN trên SiC: Lớp nền sapphire 50 μm cải thiện hiệu suất chiết xuất ánh sáng (LEE) lên 85% (so với 65% đối với tấm wafer 150 μm) bằng cách giảm thiểu hiện tượng bẫy photon. Khả năng kiểm soát TTV cực thấp (<0,3 μm) của thiết bị đảm bảo phát xạ LED đồng đều trên toàn bộ tấm wafer 12 inch, điều này rất quan trọng đối với màn hình Micro-LED yêu cầu độ đồng nhất bước sóng <100nm.

• Quang tử silicon: Các tấm silicon dày 25μm cho phép giảm tổn hao truyền dẫn 3 dB/cm trong các ống dẫn sóng, điều cần thiết cho các bộ thu phát quang 1,6 Tbps. Quy trình này tích hợp làm mịn CMP để giảm độ nhám bề mặt xuống Ra <0,1 nm, tăng hiệu suất ghép nối lên 40%.

4. Cảm biến MEMS

• Gia tốc kế: Các tấm silicon 25 μm đạt được tỷ lệ tín hiệu trên nhiễu (SNR) >85 dB (so với 75 dB của tấm 50 μm) bằng cách tăng độ nhạy dịch chuyển khối lượng thử nghiệm. Hệ thống mài hai trục của chúng tôi bù trừ cho sự chênh lệch ứng suất, đảm bảo độ trôi độ nhạy <0,5% trong khoảng nhiệt độ từ -40°C đến 125°C. Các ứng dụng bao gồm phát hiện va chạm ô tô và theo dõi chuyển động AR/VR.

• Cảm biến áp suất: Việc làm mỏng đến 40 μm cho phép đo trong phạm vi 0–300 bar với độ trễ FS <0,1%. Sử dụng liên kết tạm thời (giá đỡ bằng thủy tinh), quy trình này tránh được hiện tượng nứt vỡ tấm wafer trong quá trình khắc mặt sau, đạt được khả năng chịu áp suất dư <1 μm cho các cảm biến IoT công nghiệp.

• Sự phối hợp công nghệ: Thiết bị làm mỏng tấm bán dẫn của chúng tôi kết hợp mài cơ học, đánh bóng hóa học cơ học (CMP) và khắc plasma để giải quyết các thách thức về vật liệu khác nhau (Si, SiC, Sapphire). Ví dụ, GaN trên SiC yêu cầu mài lai (bánh mài kim cương + plasma) để cân bằng độ cứng và giãn nở nhiệt, trong khi cảm biến MEMS đòi hỏi độ nhám bề mặt dưới 5 nm thông qua đánh bóng CMP.

• Tác động đến ngành công nghiệp: Bằng cách cho phép tạo ra các tấm bán dẫn mỏng hơn, hiệu năng cao hơn, công nghệ này thúc đẩy sự đổi mới trong chip AI, mô-đun 5G mmWave và thiết bị điện tử linh hoạt, với dung sai TTV <0,1 μm cho màn hình gập và <0,5 μm cho cảm biến LiDAR ô tô.

Dịch vụ của XKH

1. Giải pháp tùy chỉnh

Cấu hình có thể mở rộng: Thiết kế buồng từ 4 đến 12 inch với chức năng nạp/dỡ tự động.

Hỗ trợ pha tạp: Công thức tùy chỉnh cho tinh thể pha tạp Er/Yb và tấm wafer InP/GaAs.

2. Hỗ trợ toàn diện

Phát triển quy trình: Chạy thử miễn phí kèm tối ưu hóa.

Đào tạo toàn cầu: Tổ chức các hội thảo kỹ thuật hàng năm về bảo trì và khắc phục sự cố.

3. Gia công đa vật liệu

SiC: Làm mỏng tấm wafer xuống còn 100 μm với Ra <0,1 nm.

Sapphire: Độ dày 50μm cho cửa sổ laser UV (độ truyền dẫn >92%@200 nm).

4. Dịch vụ giá trị gia tăng

Vật tư tiêu hao: Đá mài kim cương (hơn 2000 tấm wafer/tuổi thọ) và dung dịch CMP.

Phần kết luận

Thiết bị làm mỏng tấm bán dẫn này mang lại độ chính xác hàng đầu trong ngành, tính linh hoạt với nhiều loại vật liệu và khả năng tự động hóa thông minh, khiến nó trở nên không thể thiếu đối với tích hợp 3D và điện tử công suất. Các dịch vụ toàn diện của XKH—từ tùy chỉnh đến xử lý sau gia công—đảm bảo khách hàng đạt được hiệu quả chi phí và hiệu suất vượt trội trong sản xuất chất bán dẫn.